介绍

使用 AMD-Xilinx FPGA设计一个全连接DNN核心现在比较容易(Vitis AI),但是利用这个核心在 DNN 计算中使用它是另一回事。本项目主要是设计AI加速器,利用Xilinx的CDMA加载权重,输入到PL区的Block Ram。

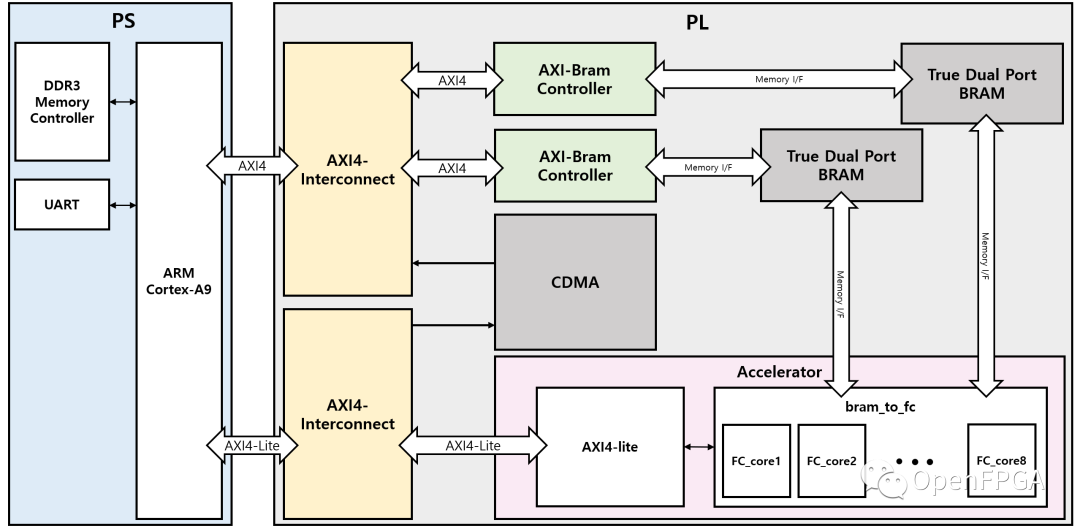

原理框图

首先,我们创建了整个系统的示意图。有两个 Block RAW 分别用于存储输入特征和权重数据。每个Block RAM 都连接到一个 CDMA ,允许 DRAM 访问 Bram。每个 Block RAM 还连接到由 8 个 FCN 内核和 FSM 组成的主加速器,控制内核的操作。

完整的激活顺序如下:

- 在 DDR 内存中存储特征和权重。

- 使用CDMA 将这些数据分别发送到block ram1 和block ram2。

- 向 FC core 发送 activate 信号,进行 FCN 计算。

- 将结果存储在 blcok ram 中。

- 重复此过程,直到完成第一层前向传播。

- 重复整个过程,将输入链接到存储在Block RAM 中的结果。

版权归原作者 碎碎思 所有, 如有侵权,请联系我们删除。