系列文章目录:FPGA原理与结构(0)——目录与传送门

一、前言

本文介绍xilinx的时钟IP核 Clocking Wizard v6.0的具体使用与测试过程,在学习一个IP核的使用之前,首先需要对于IP核的具体参数和原理有一个基本的了解,具体可以参考:

FPGA原理与结构——时钟IP核原理学习https://blog.csdn.net/apple_53311083/article/details/132497850

二、时钟 IP核定制

1、 Clocking Wizard IP核

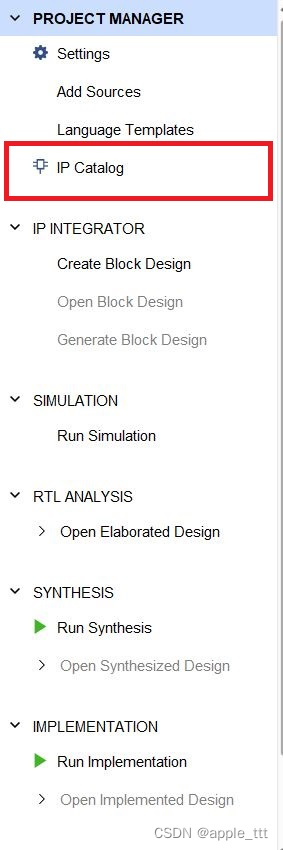

step1 打开vivado工程,点击左侧栏中的IP Catalog

step2 在搜索栏搜索clock,找到Clocking Wizard IP核

2、 IP核定制

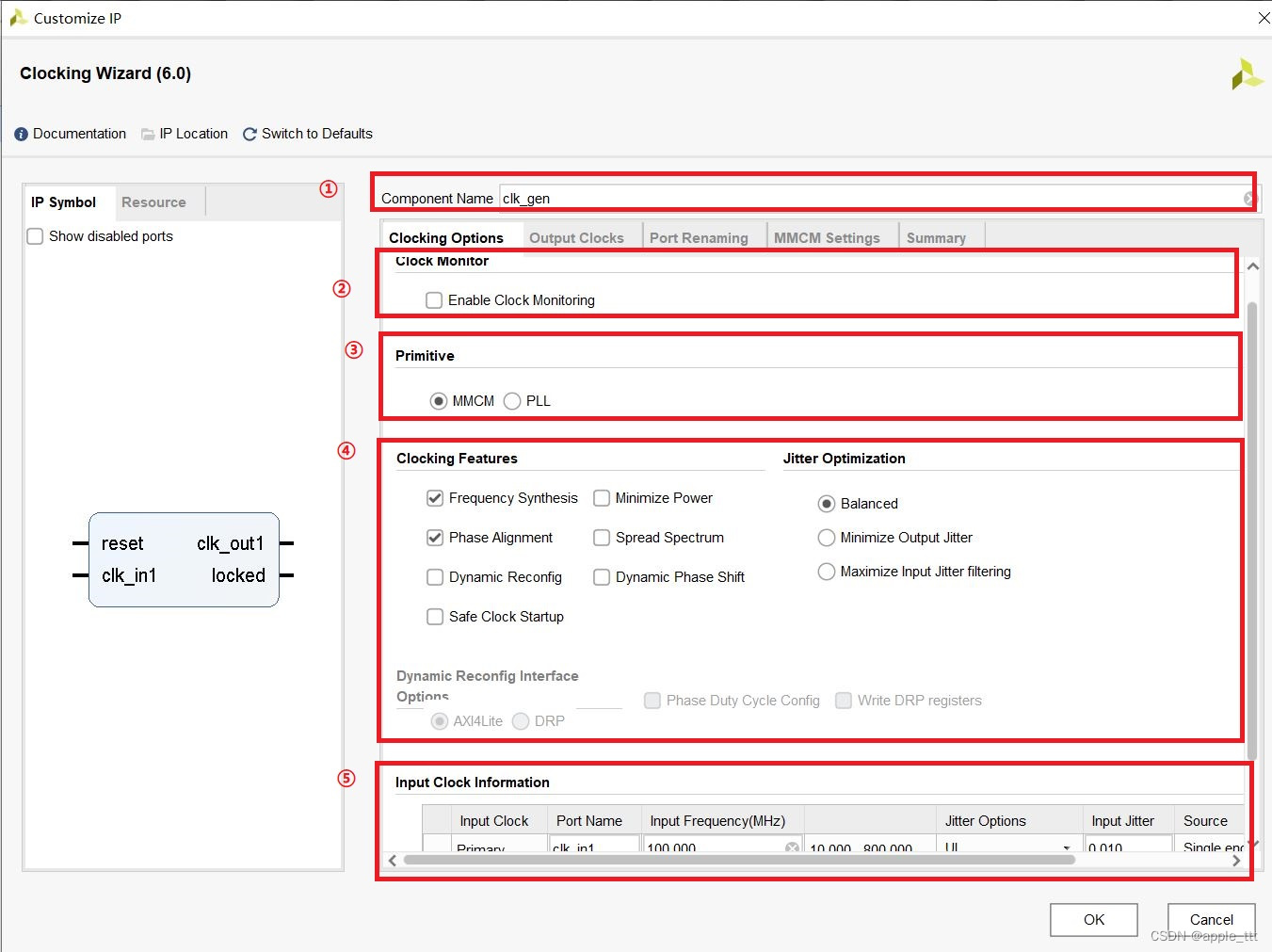

step3 Clocking Options 界面定制

① Component Name” :用于设置该IP 核的名称

② “Clock Monitor” :用来监控时钟是否停止、故障和频率变化。一般不用;

③ “Primitive” :用于选择是使用MMCM 还是PLL 来完成时钟需求,一般来说,MMCM 和PLL 都可以完成,这里保持默认选择MMCM。

④ “Clocking Features” :

- Frequency Synthesis : 表示频率综合,只有勾上才能修改想要的时钟频率。

- Phase Alignment : 相位对齐,勾选后输出时钟与输入时钟的相位是一致的

- Dynamic Reconfig : 可以通过AXI接口对时钟IP核进行动态配置,这里不适用

- Safe Clock Startup : 安全启动,在时钟稳定之前不会有输出

- Minimize Power :最小化功率,缺点是可能会影响性能

- Spread Specturm : 频谱扩展

- Dynamic Phase Shift : 动态可调相位

"Jitter Optimization " :

- Balanced : 平衡模式(默认选项),性能和功耗处于平衡状态

- Minimize Output Jitter : 输出时钟抖动最小化模式,功耗会增大,相位可能恶化

- Maximize Input Jitter filtering : 最大化输入时钟过滤,适用于输入时钟的抖动较大的情况,但是可能会导致输出时钟的抖动过大

⑤ “Input Clock Information”:选项中,把“Primary”时钟的输入频率修改为开发板的核心板上的晶振频率,source根据时钟源类型选择,单端时钟或者差分时钟,这里我们进行的是仿真测试,设置的输入时钟频率为100MHZ 。

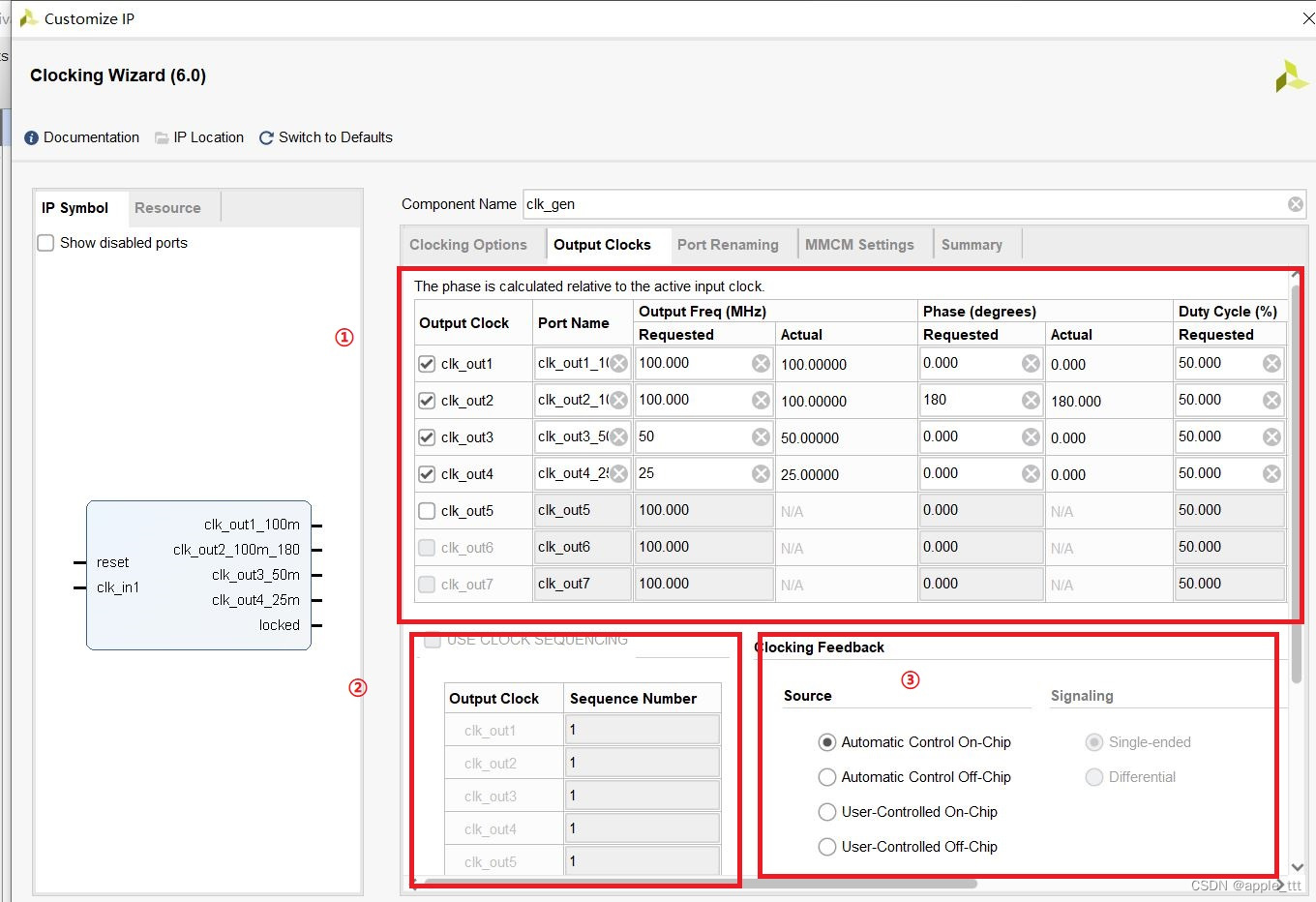

step4 Output Clocks 界面定制

① : 这里我们就可以设置我们所需要的输出时钟频率和相位了,这里我们设置了4个输出时钟,clk_out1_100m:100MHZ时钟,clk_out2_100m_180:100MHZ时钟,与clk_out1_100m不同的是,其有着180°的相位差,clk_out3_50m:50MHZ时钟,clk_out3_25m:25MHZ时钟。

② : 勾选不同信号的输出顺序,使用的前提是要在之前的界面勾选上Safe Clock Startup,这里就不适用

③ :Clocking Feedback :时钟反馈,只有在之前的界面勾选了Phase Alignment才可以使用

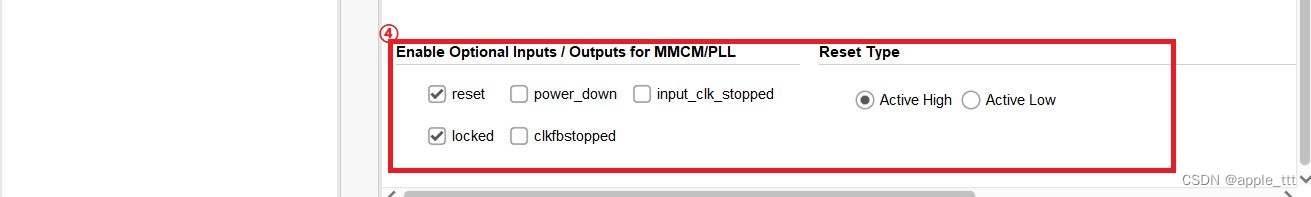

④ : 一些额外的引脚可选项,这里着重介绍一下locked :置位时表示PLL输出信号有效,平常使用PLL一定要等该信号有效

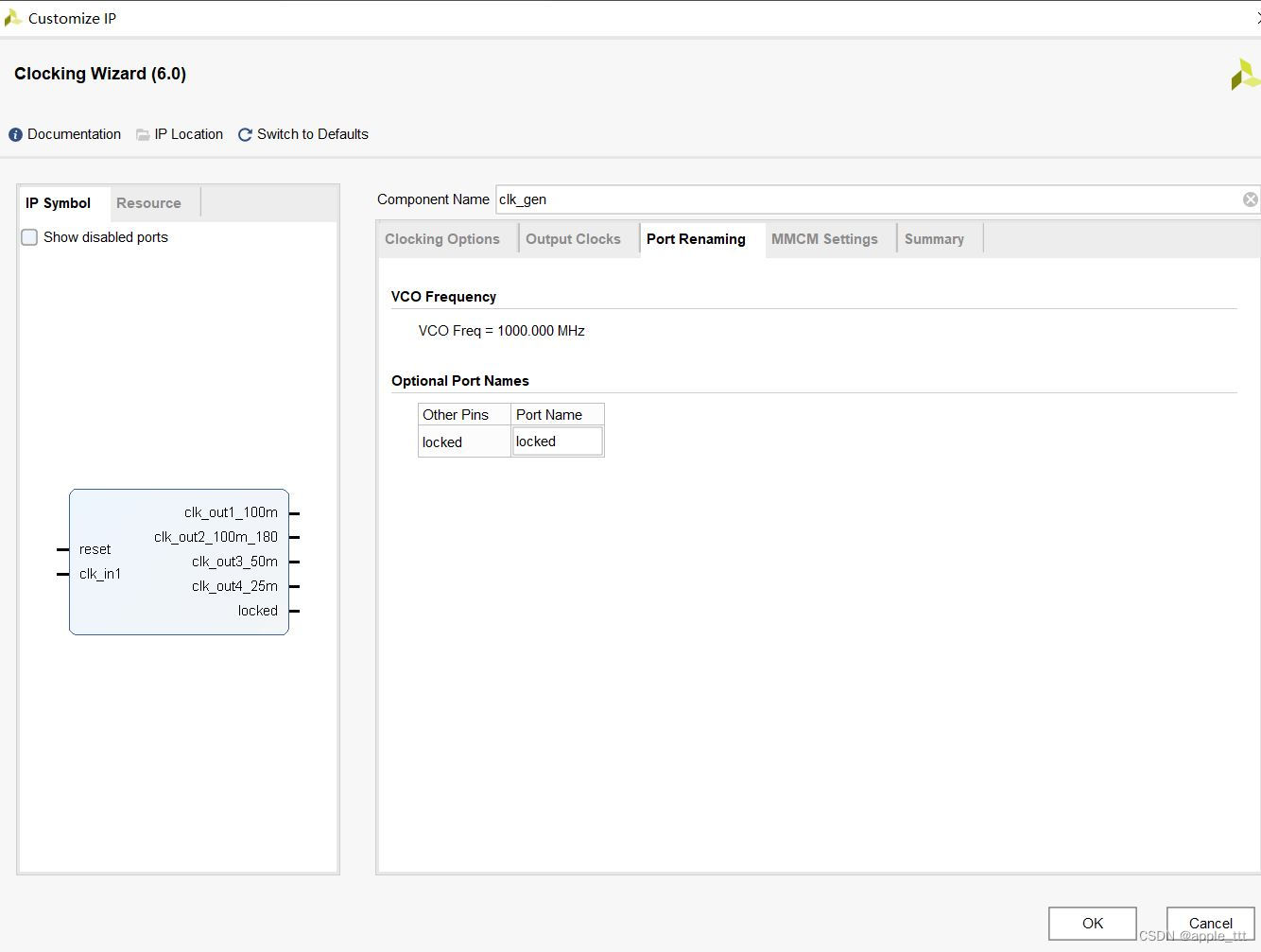

step5 Port Renaming 界面定制

输出端口信号重命名,一般不用修改。

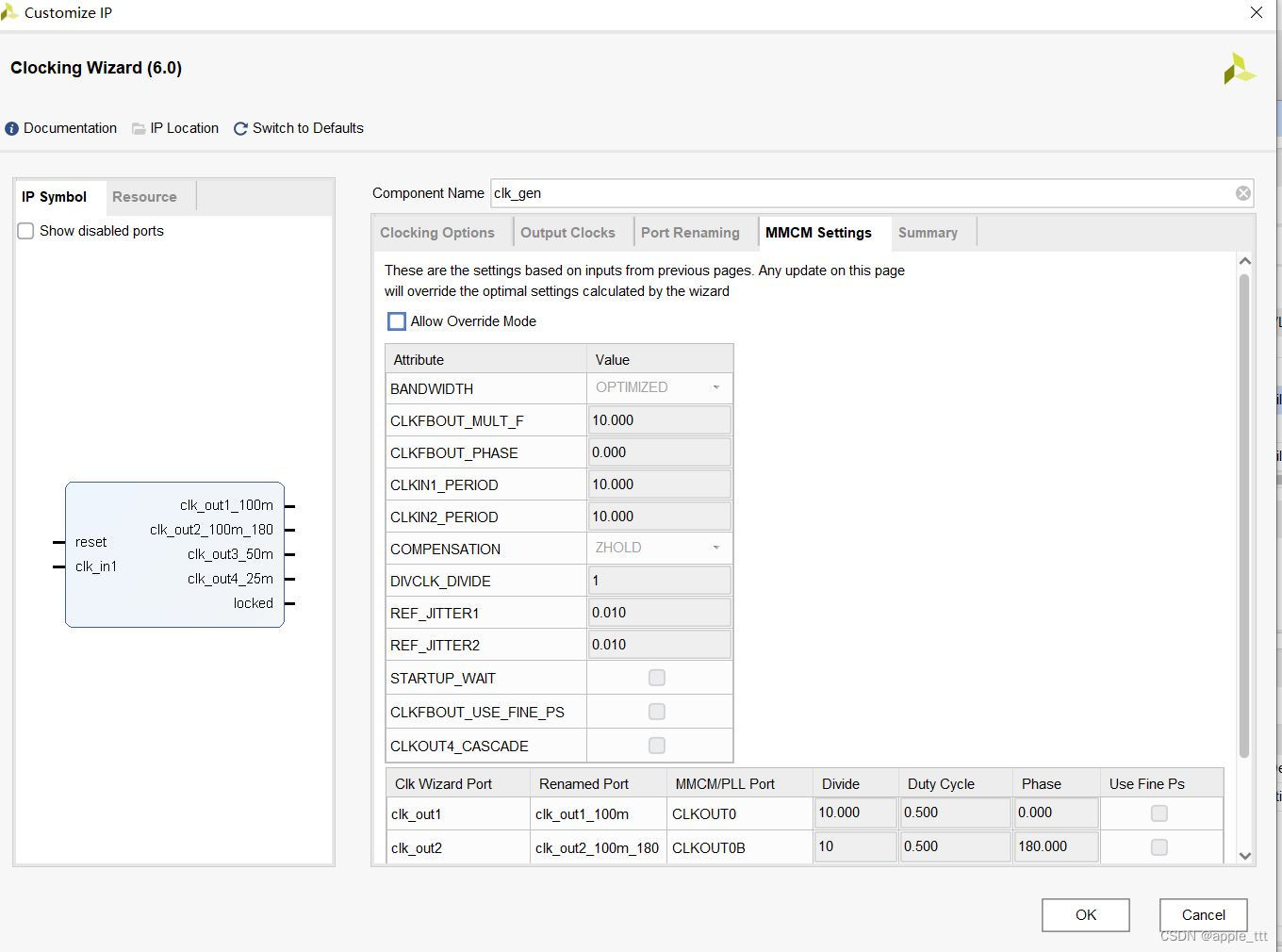

step6 MMCM Settings 界面定制

“MMCM Setting”选项卡展示了对整个MMCM/PLL 的最终配置参数,这些参数都是根据之前用户输入的时钟需求由Vivado 来自动配置的,Vivado 已经对参数进行了最优的配置,在绝大多数情况下都不需要用户对它们进行更改,也不建议更改,所以这一步保持默认即可,如下图所示。

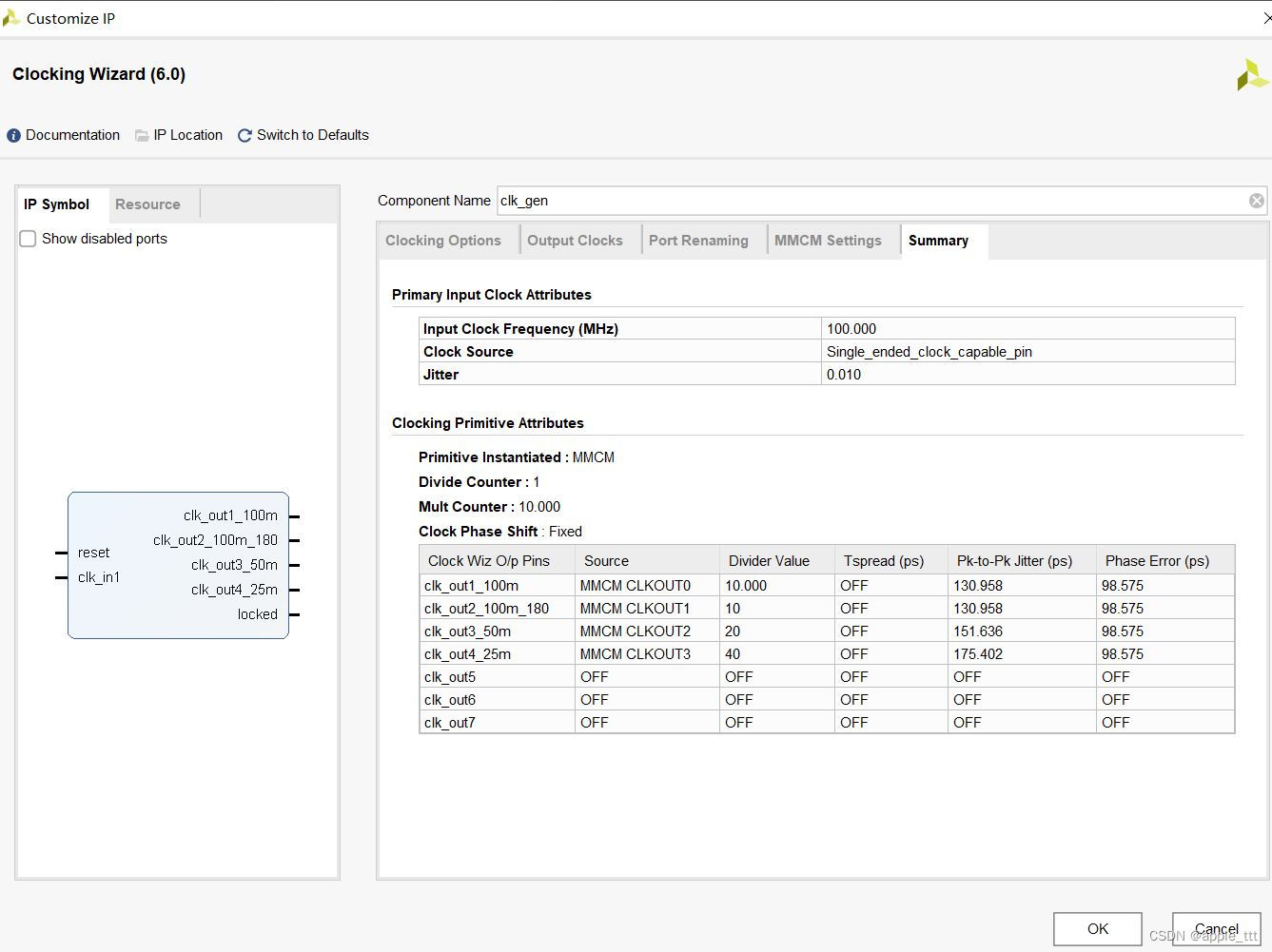

step7 Summary

最后的“Summary”选项卡是对前面所有配置的一个总结,在这里直接点击“OK”按钮即可。

3、IP核测试

首先编写顶层文件,完成对于IP核的例化

module clk_top(

input sys_clk,

input rst,

output clk_100m,

output clk_100m_180,

output clk_50m,

output clk_25m,

output locked);

clk_gen clk_gen_u1

(

// Clock out ports

.clk_out1_100m(clk_100m), // output clk_out1_100m

.clk_out2_100m_180(clk_100m_180), // output clk_out2_100m_180

.clk_out3_50m(clk_50m), // output clk_out3_50m

.clk_out4_25m(clk_25m), // output clk_out4_25m

// Status and control signals

.reset(rst), // input reset

.locked(locked), // output locked

// Clock in ports

.clk_in1(sys_clk)); // input clk_in1

endmodule

接下来进行测试文件编写:

`timescale 1ns / 1ps

module tb_clk_top();

reg sys_clk;

reg rst;

wire locked;

wire clk_100m,clk_100m_180,clk_50m,clk_25m;

always #5 sys_clk = ~sys_clk;

initial begin

sys_clk <= 1'b0;

rst = 0;

#15

rst = 1;

#10

rst = 0;

end

clk_top clk_top_u1(

.sys_clk (sys_clk),

.rst (rst),

.clk_100m(clk_100m),

.clk_100m_180(clk_100m_180),

.clk_50m(clk_50m),

.clk_25m(clk_25m),

.locked(locked)

);

endmodule

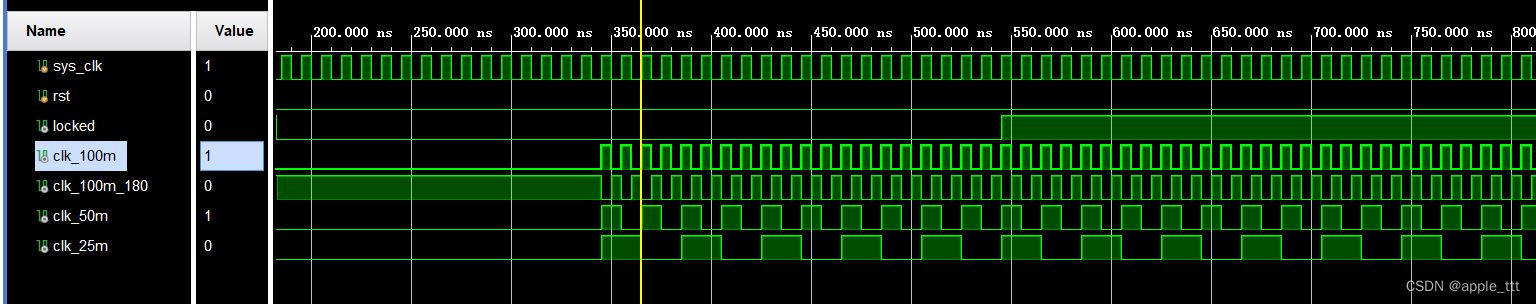

4、测试结果

可以看到,经过一段时间后,时钟输出趋于稳定,实现稳定的分频时钟输出,与我们预期的结果是一致的。

三、总结

时钟IP核在我们的FPGA设计过程中是非常常用的,一般也是我们推荐使用的一种设计方式,它可以给我们提供不同频率,不同相位的时钟输出。

版权归原作者 apple_ttt 所有, 如有侵权,请联系我们删除。