Vitis HLS简介

Vitis™HLS是一种高层次综合工具,支持将C、C++和OpenCL™函数硬连线到器件逻辑互连结构和RAM/DSP块上。

Vitis HLS可在Vitis应用加速开发流程中实现硬件内核,并使用C/C++语言代码在Vivado®Design Suite中为赛灵思器件设计开发RTL IP。

【Vitis】HLS高层次综合的优势

【Vitis】Vitis性能优化的开源库

【Vitis】基于C++函数开发组件的步骤

【Vitis】Vitis HLS2023不支持的功能特性

概述

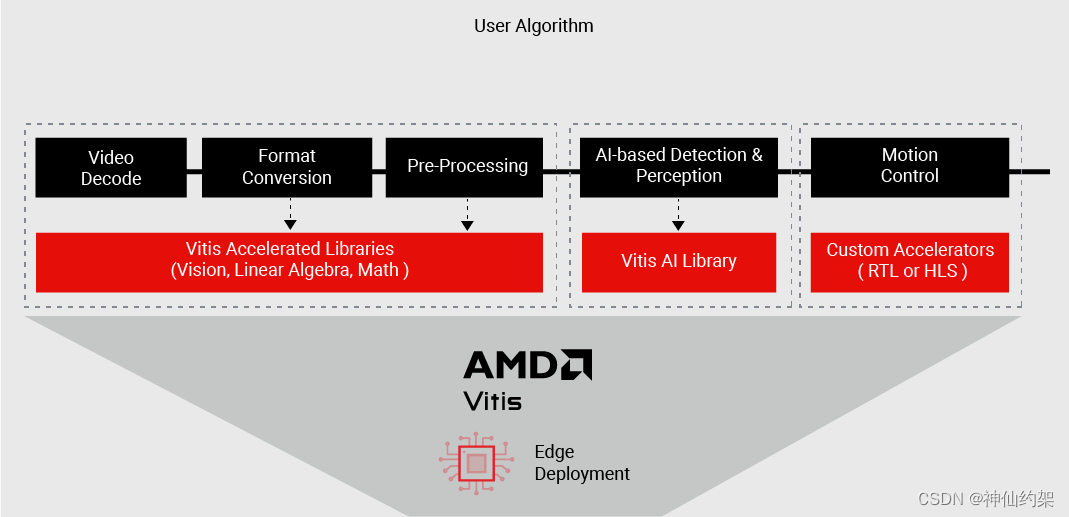

Vitis 加速库

Vitis™ 统一软件平台包括一组广泛的、性能优化的开源库,这些库提供了即开即用的加速功能,并且对现有应用实现最小化代码更改或零更改。

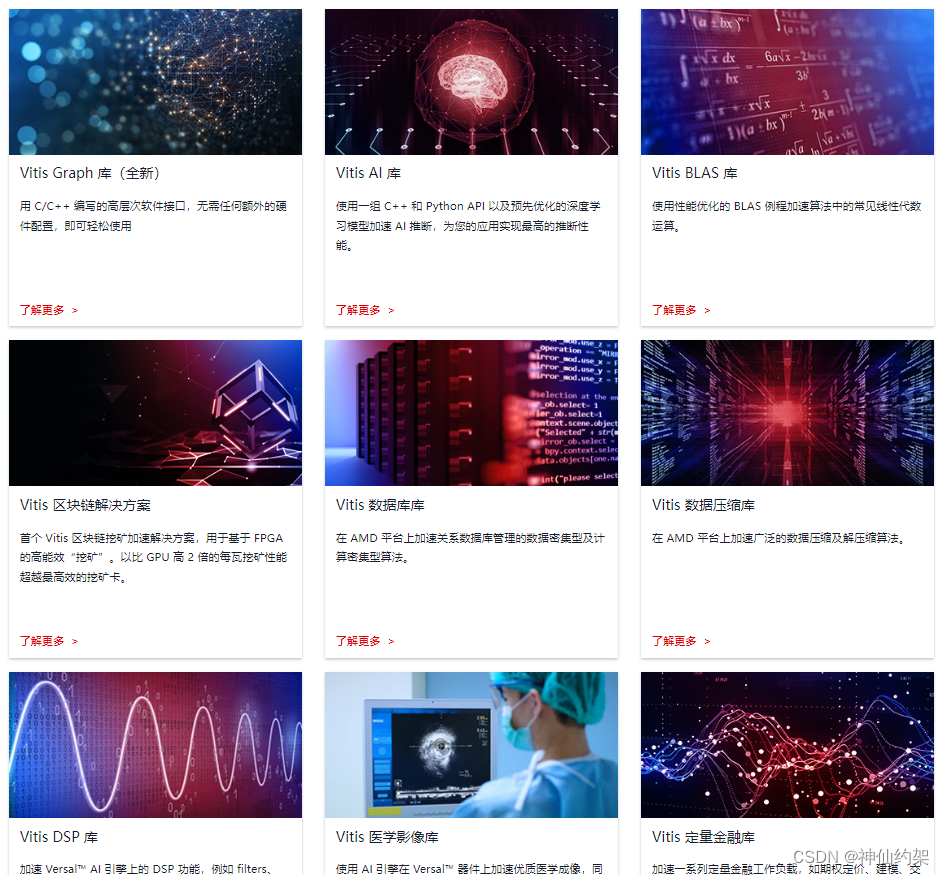

- 通用 Vitis 加速库(包括求解器、基本线性代数子程序 (BLAS)、稀疏、DSP 和实用程序)可为各种不同的应用提供一系列核心功能。

- 特定领域 Vitis 加速库为视觉及图像编解码器处理、定量金融、HPC、图形、数据库、数据分析、数据压缩等工作负载提供开箱即用的加速。

- 利用合作伙伴加速库、框架插件以及加速应用这一不断发展的生态系统,迅速启动设计,加速您的量产进程。

Vitis 库现在包含 DSP、矩阵和其它函数,这些函数针对在 Versal™ 器件的 AI 引擎部分实施进行了优化。

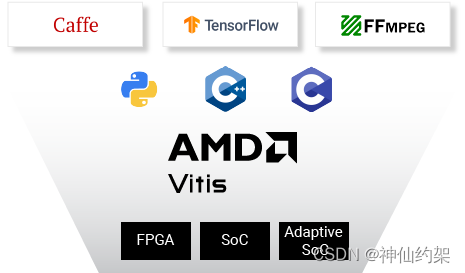

使用熟悉的编程语言

使用采用您熟悉的常用编程语言(如 C/C++)编程的 Vitis 加速库。此外,其中一些库还包括 3 级 Python 函数,例如 Vitis BLAS 库和 Vitis Quantitative Finance 库等。将 AMD 平台作为实现您应用的工具 — 在应用层面工作,将您的主要精力集中在解决您所在领域极具挑战性的问题上,并加速洞察与创新的进程。

无论您是想要加速现有 x86 主机应用代码的某些部分,还是想要开发在 AMD 嵌入式平台上部署的加速器,在您的代码中调用 Vitis 加速器库 API 或内核都可提供与任何软件库相同的抽象级别。

可扩展、灵活度高

所有开发人员都可通过 GitHub 访问 Vitis 加速器库,而且这些库可在所有 AMD 平台间扩展。使用这些优化的库开发应用并在边缘、本地或云的平台间进行无缝部署,无需重新实现加速应用。

AMD 可为您的应用带来快速原型设计和评估,您可将这些库用作即插即用加速器,在用户应用中作为 API 直接调用,满足计视觉及图像编解码器处理、定量金融、HPC、图形、数据库和数据分析等工作负载需求。

要为您的应用设计自定义加速器,可将 Vitis 库函数用作优化的算法构建块,对其进行修改,以满足您的特定需求,也可将其用作参考来完全设计您自己的加速器。选择您需要的灵活性!

将特定域 Vitis 库与 Vitis AI 库或 Vitis AI 开发套件预先优化的深度学习模型相结合,不仅可加速整个应用,而且还可达到整个系统级的功能及性能目标。

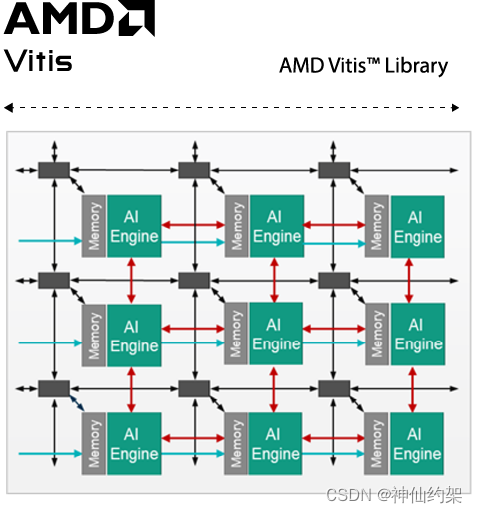

针对 Versal AI 引擎优化的 Vitis 库函数

位于 Versal 器件的 AI 引擎可为基于矢量的算法提供极高的计算密度。

以下库添加了 AI 引擎:

- Vitis DSP 库

- Vitis 视觉库

- Vitis Solver 库

AI 引擎代码位于“AIE”目录(位于 AIE 专用函数的 L1 下以及 AIE 和 Pl 代码组成的函数的 L2 下)下。

注:如欲了解更多详情,请参阅各库的页面。

库文件组织

一个 Vitis 库通常有三个级别 (L1/L2/L3) 的函数:

L1 原语

- 设计内核的基本算法函数(HLS 函数)

- 可以自定义,也可以与其它原语及内核组合

- 需要用 Vitis 工具构建和编译

L2 内核

- 带所需接口及编译器指令的性能优化内核

- 必要时,可使用 Vitis 工具定制和构建加速器映像

- 通过与 Xilinx 运行时库 (XRT) 集成来管理的初始化和数据传输

L3 软件 API

- 可在主机应用中直接调用的高层次软件 API

- API 可调用预先构建的 FPGA 映像(为特定平台提供)

- 用户可自定义,也可重新构建

库

Vitis 视觉库

在 AMD 平台上为 ADAS、视频监控和数据中心等开发和部署加速的计算机视觉及图像处理算法。

开始设计

文档与下载

- 下载所有 Vitis 库

- 所有 Vitis 库文档

了解更多

- AMD Xilinx 合作伙伴库和解决方案

- Vitis 环境深入教程

网络研讨会点播

- 使用 Vitis 加速库开发应用

- 比较图算法在 AMD Xilinx FPGA 和 Nvidia GPU 上的性能

版权归原作者 神仙约架 所有, 如有侵权,请联系我们删除。