代码设计规范的重要性

经过一段的工作积累已经慢慢进入了提高和进阶的阶段,在这篇博客里多聊一聊在现实工作中的话题,比如代码规范以及如何尽快接手前人代码,快速定位项目问题。

显然每个FPGA工程师的设计理念和代码风格很多情况下有一些差别,比如有的FPGA工程师青睐于Gvim编辑器下的计数器和状态机模板,有的则用习惯了Notepad++、UE等其他编辑器,代码风格会存在一些不同;也有的模块划分理念很弱,一个.v文件吧啦吧啦写了好几千行,包括了底层协议实现、上游命令解析、数据计算处理等等很多内容,然后代码放了一段时间后,写代码的当事人自己再看都不知道哪里对哪里;还有的命名不规范,代码逻辑混乱,导致可读性差,透过代码可以感受到同事是想到哪里写到哪里,在编码之前脑子里没有个整体思路;最后崩溃的地方可能是前人代码逻辑也做了大量Testbench仿真测试,但是还有些隐形的问题没有暴露出来,而实际落地的时候又出现了问题,回头再去检查程序,如同看到一堆if else、flag、定时器的单片机裸机程序一样让人头疼,但是接手后因为情况紧急,还被指定在deadline前搞定,那么当时心情一定非常复杂的。

一般比较大型项目按照模块划分可能会有很多个FPGA工程师一起完成,然后再对接好各个模块的信号;也有不少中小型企业为了降低用人成本,甚至写ARM和FPGA的都是同一个人;还有一些工程师利用业余时间和其他人创业,最后变成写程序和画板子都是一个人在做,那么不管与他人合作完成项目也好,还是自己独立承担项目也好,代码设计规范一定是非常重要的事情,优秀的代码风格会让大家事半功倍!

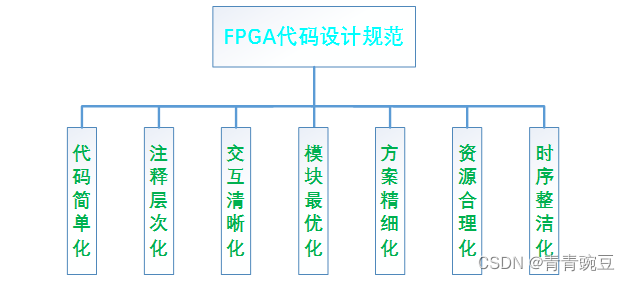

笔者也在这里简单总结了下,抛砖引玉,其实说到底,不管怎么样的编程风格或者书写习惯,如果大家在编程的时候可以有意识地做到以下这几点都是非常棒的,满足了代码的设计规范同时也大大提高了工作效率。

一、代码简单化

大部分初学者可能觉得代码写得越复杂越可以体现编程水平,笔者最开始学习Verilog的时候也是这样想的,看到逻辑复杂的代码虽然不明觉厉,但是仍然心生崇拜。可事实上却不是这样的,当项目复杂度越来越高,代码都需要经过多轮的审核等才能被应用在项目工程里,如果大家写得代码都非常复杂繁琐,那么后期带来重用的工作量是非常巨大的,也非常不容易理解当事人的想法,所以请大家编程的时候,尽量去使用常见的基本语法,也有利于工具的资源优化,对于复杂功能的模块理清楚逻辑,可以先用前面学习到的TimeGen绘制各个信号的波形图,分析明白后再动手编程,从而减少了语句之间的耦合带来程序设计上的二义性。

二、注释层次化

项目工程中代码越复杂,注释的必要性也就越大,注释层次化可以提高其他人对整个代码的理解,让其很快能理解到各个模块以及信号名的意义,笔者建议朋友们,在编写代码的时候,如果可能的话可以把每个模块的具体功能逐一标注出来,然后每个子模块的子步骤也标注出来,这样既满足了FPGA设计中自顶向下的设计理念,也极大地增加了代码的可读性,让其他人接手后很快就能了解到你的设计意图。

三、交互清晰化

交互清晰化主要是指模块和模块之间的接口信号、模块内子模块的交互清晰明了,容易理解没有歧义,不需要来回去猜想去验证,同时随着当前数字电路设计越来越复杂,一个项目里面每个人需要写的代码数量也越来越多,在不同人写的模块之间又需要彼此接口信号的配合,这里显然都需要理解对方的意图,否则就容易出问题。笔者建议最好由公司制定或者同事间多协商一些规则,接口处的信号名称最好都统一化,信号功能描述明确方便理解,比如din、din_vld、dout、dout_vld、rdy、sop、eop、req、ack等等,让大家一眼看去就明白什么意思。

四、模块最优化

任何再复杂的系统也都是由一个个子模块组合在一起完成的,如果模块划分不合理,必然会出现很多后期让人头疼的问题,有很多血淋淋的教训,比如出现模块间耦合太多,导致系统健壮性不够;本应该多个模块实现的功能强行放到一个模块,导致代码可读性很差;前期考虑欠缺经验不足,导致代码稳定性很低等等。

五、方案精细化

设计方案是编写代码的前提条件,越是功能复杂的项目,越需要在前期把方案明确化,把思路清晰化,可能大家在初学FPGA的时候,都希望多编写代码,多敲多练,这本身是很好的想法,但是当走到工作岗位后,这种思想就不合适了,磨刀不误砍柴工,想好再动手永远比一抹黑地生干生做要效率高很多。

举个现实的例子,比如朋友们接手一个新项目,涉及到了数字信号处理、接口通信协议、控制外围器件、与ARM或者DSP建立通信机制等等实际需求,这时候就不要上来就写代码了,请多去对需求分析,多去画设计图纸,前期增加方案时间,后期减少返工时间。笔者曾自己独立完成过一个较为复杂的项目,前期方案验证花了3个半月包括核对工作量,核实可行性,查阅手册、了解细节等等,后期编程用2个月的时间一直在编写代码、仿真验证、上板调试,因为有些东西是第一次接触,所以做起来有时候会出现卡壳的情况,但是前期方案明确指导编程,后期几乎每周都可以看到实打实地进展。

前期方案设计应该更细节化,需要达到指导编程的目的,同时也需要验证一些可行性。如果是大企业也会组织方案评审等,这时候就需要把方案写得更加明了易懂,其中包括了:功能描述、架构实施、模块划分、实现细节、时序波形、接口描述等等,甚至一些公司内部也有一套很细致的评审方案。

六、资源合理化

方案设计的同时不可避免地要提到资源的使用程度,因为资源的使用程度最后决定了芯片选型和外围电路,就如嵌入式研发中那句经典的话一样:需求决定硬件,硬件决定软件,如果芯片选型不合适,那么后期FPGA工程师也巧妇难为无米之炊,导致项目延期等一系列的问题。

资源占用情况是评估选用哪种器件的前提,这里也很关键,就如前面Xilinx Artix7硬件设计小节提到过的一样,嵌入式产品软件和硬件是紧密结合在一起的,在芯片选型的时候,请大家注意以下两点,也是在项目工程中积累到的经验:1.尝试去评估最恶劣情况下的资源使用量,很多新的项目在初期往往需求不算很多,但是随着产品的更新,对软件上面的需求也越来越大,这时候可以折中地选择性价比最高的芯片;2.增加一些裕量,在整体方案评估完成后,评估整个设计对FPGA芯片各种逻辑资源的使用率,适当增加一些使用裕量。

七、时序整洁化

时序设计是Verilog代码编写的前提,优秀的时序逻辑是设计出来的,而不是后期生搬硬凑出来的。所以大家在学习实践过程中,需要有意识地多加积累一些优秀的时序设计思路,比如典型的有流水线处理的思想,流水线设计从某种角度来说,可以很大程度上提高整个系统设计的频率,常用于高速信号处理领域,如果一个设计可以细分为若干步骤进行处理,而且整个数据处理过程又是单向处理的,即没有反馈运算或者迭代运算等需要双向处理的,通俗地说前一个步骤的输出即为下一个步骤的输入,这时候就可以考虑采用流水线设计的方法来大大提高整个系统的工作频率。

在很多高速信号处理领域都运用了流水线设计,如高速接口通信、多路信号采集、图像加速处理等系统。举个例子,在一个高速接口处理的系统中,可以设计第一个时钟周期进行数据接收、第二个时钟周期进行数据处理、第三个时钟周期进行数据拼接、第四个时钟周期进行数据校验等等。

FPGA代码设计规范

标签:

fpga开发

本文转载自: https://blog.csdn.net/wandou0511/article/details/127706826

版权归原作者 青青豌豆 所有, 如有侵权,请联系我们删除。

版权归原作者 青青豌豆 所有, 如有侵权,请联系我们删除。