文章目录

学习芯片: EP4CE6F17C8

一、使用verilog实现电亮fpga板上的四个灯

verilog代码如下:

module led1(

output wire [3:0] led_on

);

assign led_on = 4'b1111 ;

endmodule

配置引脚,查看芯片的指导书:

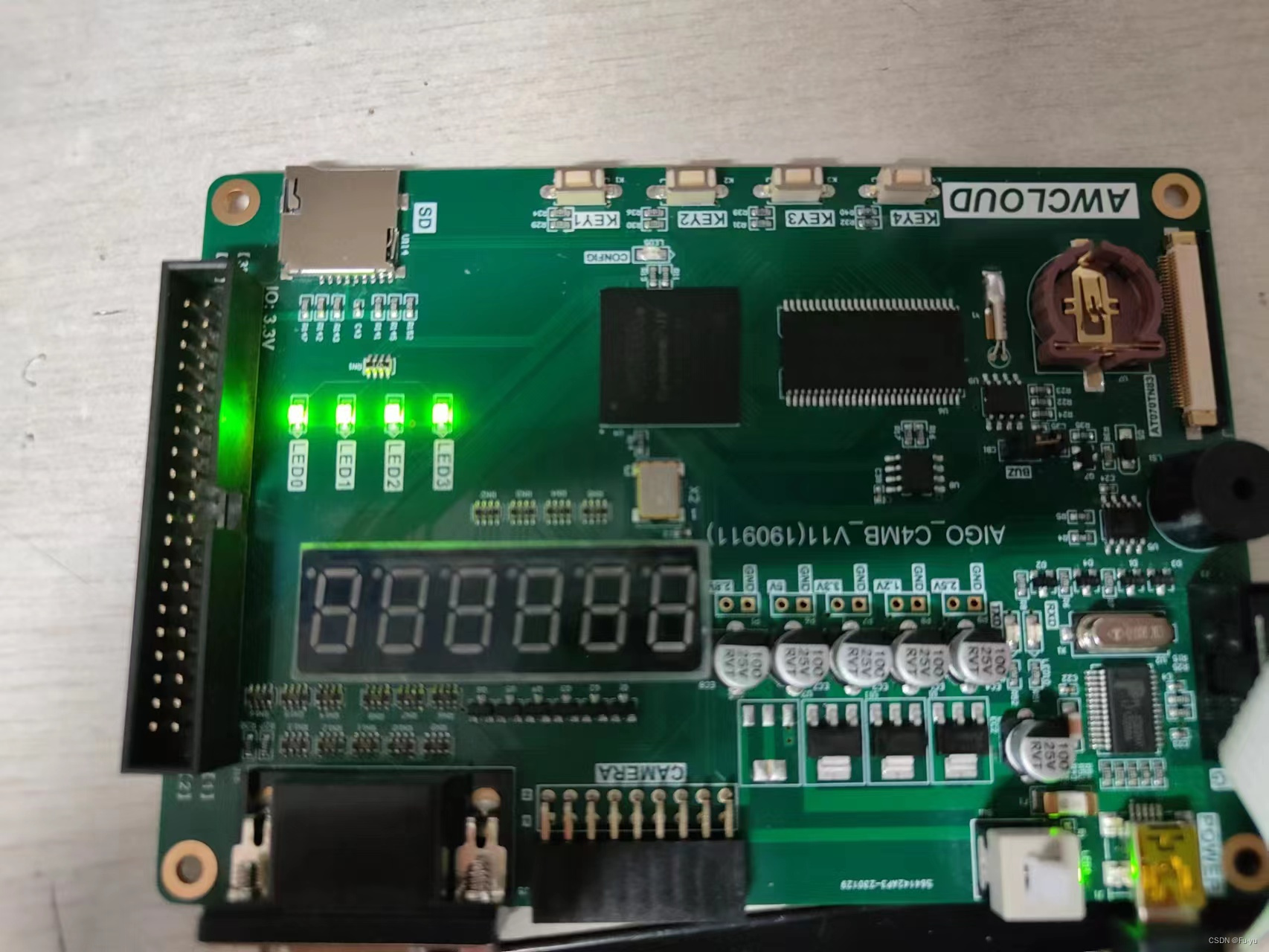

烧录运行结果如下:

如图我们可以看见开发板上四个led灯同时被电亮。

二、进阶——使led灯间隔一秒闪烁

代码如下:

module led1(

input wire clk,//时钟信号,50MHz

input wire rst_n,//复位信号,下降沿有效

output wire [3:0] led_on

);

parameter MAX1S = 26'd50_000_000;

reg [25:0] cnt1s;//计数寄存器器1s

reg [3:0] led_r;//led信号寄存器

always @(posedge clk or negedge rst_n) begin

if (!rst_n ) begin//复位,重新计数

cnt1s<=26'd0;

end

else if (cnt1s == MAX1S-1'b1)begin//记到最大数,重新计数

cnt1s<=26'd0;

end

else begin//其他情况+1

cnt1s <= cnt1s + 1'd1;

end

end

always @(posedge clk or negedge rst_n) begin

if (!rst_n ) begin//复位

led_r = 4'b0000;

end

else if (cnt1s == MAX1S-1'b1)begin//记到最大数,翻转

led_r = ~led_r;

end

else begin

led_r = led_r;

end

end

assign led_on = led_r;

endmodule

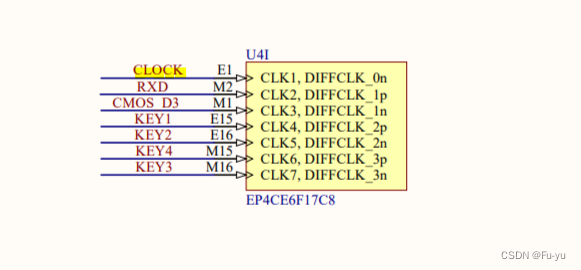

配置引脚,查看clock和key的引脚:

运行结果如下图:

此时可以看见四个led灯同时闪烁。

三、进阶——流水灯及跑马灯实现

流水灯代码实现:

module led1(

input wire clk,//时钟信号,50MHz

input wire rst_n,//复位信号,下降沿有效

output wire [3:0] led_on

);

parameter MAXS = 25'd25_000_000;

reg [24:0] cnt1s;//计数寄存器器0.5s

reg [3:0] led_r;//led信号寄存器

always @(posedge clk or negedge rst_n) begin

if (!rst_n ) begin//复位,重新计数

cnt1s<=26'd0;

end

else if (cnt1s == MAXS-1'b1)begin//记到最大数,重新计数

cnt1s<=26'd0;

end

else begin//其他情况+1

cnt1s <= cnt1s + 1'd1;

end

end

always @(posedge clk or negedge rst_n) begin

if (!rst_n ) begin//复位

led_r = 4'b0001;

end

else if (cnt1s == MAXS-1'b1)begin//记到最大数,翻转

led_r = {led_r[2:0],led_r[3]};

end

else begin

led_r = led_r;

end

end

assign led_on = led_r;

endmodule

实验效果图如下:

此时可以看见led灯依次闪烁。

跑马灯代码:

module led1(

input wire clk,//时钟信号,50MHz

input wire rst_n,//复位信号,下降沿有效

output wire [3:0] led_on

);

parameter MAXS = 25'd25_000_000;

reg [24:0] cnt1s;//计数寄存器器0.5s

reg [3:0] led_r;//led信号寄存器

always @(posedge clk or negedge rst_n) begin

if (!rst_n ) begin//复位,重新计数

cnt1s<=26'd0;

end

else if (cnt1s == MAXS-1'b1)begin//记到最大数,重新计数

cnt1s<=26'd0;

end

else begin//其他情况+1

cnt1s <= cnt1s + 1'd1;

end

end

always @(posedge clk or negedge rst_n) begin

if (!rst_n ) begin//复位

led_r = 4'b0001;

end

else if (cnt1s == MAXS-1'b1)begin//记到最大数,翻转

led_r = {led_r[2:0],~led_r[3]};

end

else begin

led_r = led_r;

end

end

assign led_on = led_r;

endmodule

实验效果图如下:

版权归原作者 Fu-yu 所有, 如有侵权,请联系我们删除。