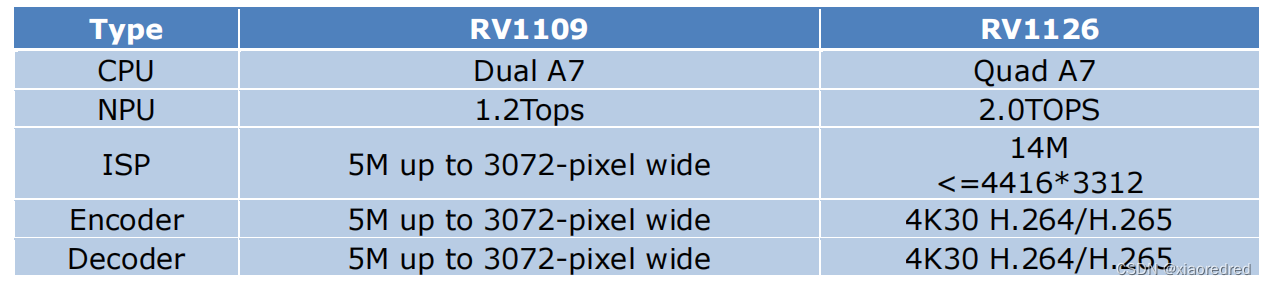

RV1109与RV1126参数

主要区别

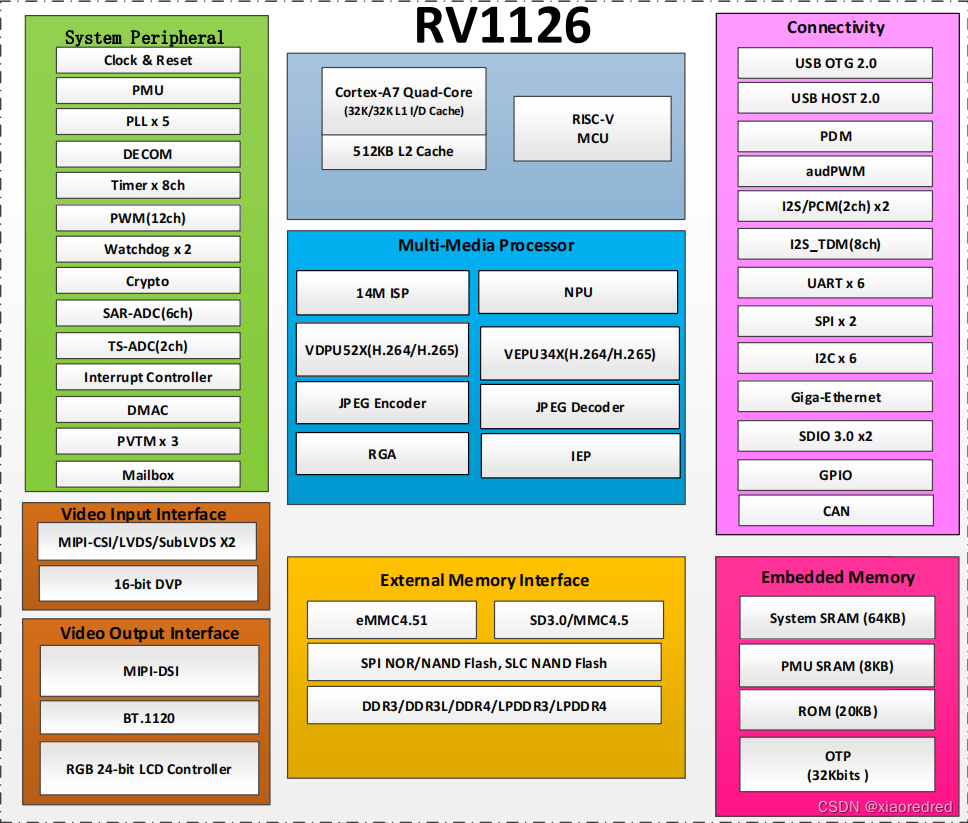

RV1126处理器(例子)

四核核 Cortex-A7,ARM架构V7-A指令,独立Neon SIMD(一种高级单指令多数据扩展指令集,可执行并行数据处理),与独立FPU(浮点计算)。(RV1109双核A7)

每核有32KB L1 I-Cache(一级指令高速缓存),32KB L1 D-Cache(一级数据高速缓存)

512KB L2 Cache(二极高速缓存)

CPU核心独立供电,可以单独关闭开启。

DVFS 即动态电压频率调整,动态技术则是根据芯片所运行的应用程序对计算能力的不同需要,动态调节芯片的运行频率和电压(对于同一芯片,频率越高,需要的电压也越高),从而达到节能的目的。

视频输入接口

接口和视频输入处理单元

- 两个MIPI CSI/ LVDS/SubLVDS接口,每个4个通道,MIPI CSI最大数据速率为每通道2.5Gbps,LVDS/SubLVDS最大数据速率为每通道1Gbps。

- 一个8/10/12/16位标准DVP接口,最多为150MHz的输入数据。

- 支持BT.601/BT.656年和BT.1120个VI接口。

- 支持pixel_clk、hsync、vsync的极性可配置。

ISP(图像处理算法)

- 最大分辨率为1400万像素(4416x3312)(RV1109为500万像素)

- DVP输入: ITU-R BT。601/656/1120,原始8/10/12/16生,YUV422

- MIPI输入: RX数据通道x1/x2/x4,原始8/原始10/原始12,YUV422

- 3A: 包括AE/直方图、AF、AWB统计输出

FPN:固定模式噪声消除BLC:黑色水平校正DPCC:静态/动态缺陷像素簇校正LSC:镜头避光校正- Bayer-NR:空间拜耳原始去噪,2DNR

- HDR:3/2帧合并到高动态范围

- TMO:3/2帧合并视频音调映射

- WDR:一帧宽动态范围音调映射

- Debayer:高级自适应去马赛克色差校正

- CCM/CSM:颜色校正矩阵;RGB2YUV等

- Gamma: Gamma输出校正

- Dehaze/Enhance:自动去除和边缘增强

- 3DLUT:面向客户的3D调试板

- LDCH:在水平方向上的镜头失真

- Output Scale3:支持降低等级3(W0<3264;W1<1280;W2<1280)

- Output Scale2:支持降低级别2(W0<1920;W1<1920)

- 输出(FBC):支持YUV422/420与帧缓冲区压缩

- 3DNR:在YUV中的高级时间噪声降低

- 2DNR:YUV中的高级空间降噪

- Sharp:图片锐化和边缘增强在YUV

- ORB:面向快速旋转的摘要,一种特征点检测方法

- FEC:更大的镜头失真和鱼眼矫正

- CGC:颜色配域压缩,YUV全范围/限制范围转换

视频编解码

视频解码器

- 实时解码H.264和H.265

- H.265的Main和Main10配置文件,最高5.0级和4096x2304@30fps

- Baseline, main, high, high10 and high 4:2:2(没有MBAFF),高达5.1级和4096x2304@30fps

视频编码器

- 实时UHD H.265/H.264视频编码 (3840x2160)

- I-/p帧和SmartP参考

- 五种比特率控制模式(CBR、VBR、FixQp、AVBR和QpMap)

- 最多可达100 Mbit/s的输出比特率

- 支持ROI(无限制)编码;

- 高规格的H.264,高达5.1级和4096x2304@30fps

- 主流的H.265,高达5.0级和4096x2304@30fps

- 支持多流编码

- 3840 x 2160@30帧ps+1080p@30帧ps编码

- 3840 x 2160@30编码+ 3840 x 2160@30帧/秒解码

- 输入数据格式:

- YCbCr 4:2:0 planar

- YCbCr 4:2:0 semi-planar

YCbYCr 4:2:2CbYCrY4:2:2 interleaved- RGB555 and BGR555

- RGB565 and BGR565

- RGB888 and BRG888

- RGB101010 and BRG101010

- 一个隔离的电压域来支持DVFS

JPEG编解码器

- JPEG编码器

- 基线(DCT顺序)

- 编码器的大小从96x96到8192x8192(67万像素)

- 每秒9000万像素

- JPEG解码器

- 解码器大小从48x48到8176x8176(66.8Mpixels)

- 高达每秒7600万像素

神经处理单元

- 神经网络加速引擎,处理性能高达2.0TOPS

- 支持整数8,整数16的卷积运算

- 支持深度学习框架:TensorFlow, TF-lite, Pytorch, Caffe, ONNX, MXNet, Keras, Darknet

- 支持OpenVX API

- 一个隔离的电压域来支持DVFS

存储器组织

- 内部芯片存储器

- BootRom(启动片内存储)

SYSTEM_SRAM在VD_LOGIC的电压域中- PMU_SRAM在VD_PMU的电压域内的低功率应用

- 外部芯片外存储器

- DDR3/DDR3L/DDR4/LPDDR3/LPDDR4-2133

- SPI闪存

- eMMC

- SD卡

异步Nand闪存

内部存储器

- 内部BootRom

- 支持从以下设备启动系统: FSPI Flash 接口 eMMC 接口 SDMMC 接口 Async Nand 接口

- 支持系统代码下载: USB OTG 接口(设备模式)

- SYSTEM_SRAM :64KB

- PMU_SRAM:8KB

外部内存或存储设备

- 双倍速率同步动态随机存储器(DDR3/DDR3L/DDR4/LPDDR3/LPDDR4-2133)

- 兼容JEDEC标准

- 与DDR3/DDR3L/DDR4/LPDDR3/LPDDR4-2133兼容

- 支持32位数据宽度,2片(芯片选择),每个片最大为4GB寻址空间,总寻址空间为4GB(最大)

- 低功耗模式,如对SDRAM的断电和自刷新

- eMMC(内嵌式多媒体存储卡)

- 与标准的iNAND接口兼容

- 兼容eMMC规范4.51

- 支持三种数据总线宽度:1位、4位或8位

- 支持高达HS200(HS200就是在clk为200M的频率下进行传输数据,对应还有hs400);但不支持CMD Queue(命令队列)

- SD/MMC(安全数字多媒体存储卡)

- 兼容SD3.0,MMC ver4.51

- 数据总线宽度为4位

- FSPI(灵活串行外设接口 )

- 支持串口flash设备之间的数据传输

- 支持x1、x2、x4个数据位模式

- 支持2个芯片选择

- Nand Flash接口

- 支持异步nand闪存

- 数据总线宽度为8位

- 支持1个芯片选择

- 支持LBA nand闪存

- 高达16bits/1KB硬件ECC(差错检测和修正算法)

- 支持可配置的接口定时

系统组件

- RISC-V 单片机

- 32位微控制器核心与RISC -V ISA(指令集架构)

哈佛架构,独立的指令和数据存储器指令集是带有M和C扩展的RV32I集成可编程中断控制器(IPIC),所有123条IRQ线连接到Cortex-A7的GIC也连接到RISC -V单片机集成的调试控制器与JTAG接口

- CRU(时钟和复位单元)

- 支持针对各个组件的时钟门控控制

- 一个振荡器与24MHz时钟输入

- 支持全芯片全局软复位控制,也支持各部件单独软复位

- PMU(电源管理单元)

- 支持5个单独的电压域:VD_CORE/VD_LOGIC/VD_PMU/VD_NPU/VD_VEPU

- 支持14个独立的电源域,可以通过软件根据不同的应用场景断电

- 多种可配置工作模式,通过不同频率或自动时钟门控制或电源域开关控制节省电源

- Timer(定时器)

- 支持6个64位定时器,支持基于中断的非安全应用程序操作

- 支持2个64位定时器,基于中断的操作,用于安全应用程序

- 支持两种操作模式:自由运行和用户定义的计数

- 支持计时器的工作状态可检查

- PWM(脉宽调制)

- 支持12个片上pwm (PWM0~PWM11),基于中断操作

- 可编程的预缩放操作总线时钟,然后进一步缩放

- 嵌入式32位计时器/计数器设备

- 支持捕获模式

- 支持连续模式或单次模式

- 提供参考模式,并输出各种占空比波形

- 针对PWM3、PWM7和PWM11的红外应用进行了优化

- Watchdong(看门狗)

- 32位看门狗计数器

- 计数器数量从预设值减少到0,以指示发生超时

- 当发生超时时,WDT可以执行两种类型的操作: 生成一个系统重置 首先生成一个中断,如果在第二次超时发生时服务例程没有清除该中断,则生成一个系统重置

可编程复位脉冲长度总共16个定义的主超时时间范围一个非安全应用程序看门狗一个看门狗安全应用程序

- 中断控制器

支持来自不同组件的128个SPI中断源输入支持16个由软件触发的中断每个Cortex-A7分别有两个中断输出(nFIQ:快速中断请求;nIRQ:标准中断请求),两者都是低水平敏感的每个中断源支持不同的中断优先级,并且始终是软件可编程的

- DMAC(Direct Memory Access Channel 直接存贮器存取通道)

基于微码编程的DMA支持链表DMA功能,完成分散-聚集传输(可以从不同缓存区读取或写入数据,不需要一整块连续的存储区域)支持内存到内存、内存到外设、外设到内存的数据传输类型使用中断输出信号来指示各种DMA事件的发生一个嵌入式DMA控制器DMAC功能: 支持8通道 来自外设的27个硬件请求 2中断输出 支持每个DMA通道的TrustZone技术和可编程安全状态

- 安全系统

- 密码引擎 支持SM2/SM3/SM4密码 支持SHA-1,SHA-256/224,SHA-512/384,MD5硬件填充 支持链接列表项(LLI)DMA传输 支持AES-128 AES-256加密和解密密码 支持AESECB/CB/CB/CFB/CTR/CTS/XTS模式 支持DES & TDES加密和解密密码 支持DES/TDES ECB/OFB/CFB模式 支持4096位PKA数学操作RSA/ECC 支持8通道配置支持256位TRNG(真随机数生成)输出

- 支持对所有DDR类型的数据置乱

- 支持安全OTP(一次性可编程序)

- 支持安全调试

- 支持安全操作系统

- Maibox(一种用于在多个进程之间传递消息的同步原语。它类似于一个缓冲区,可以存储多个消息,并且可以在不同的进程之间进行读取和写入。使用SystemVerilog邮箱可以实现进程之间的通信和同步,从而提高系统的并发性和可靠性。)

- SoC中的一个Mailbox服务于A7和RISC-V MCU的通信

- 每个Mailbox服务支持四个Mailbox元素,每个元素包括一个数据字,一个命令字寄存器和一个可以表示一个中断的标志位

- 提供32个锁寄存器供软件使用,以指示Mailbox是否被占用

- DECOM(decompressing 解压)

- 支持解压缩GZIP文件

- 支持解压缩LZ4文件,包括LZ4框架格式的一般结构和遗留框架格式

支持以Deflate格式解压数据支持ZLIB格式压缩数据支持完全中断和错误中断输出在LZ4解压过程中支持哈希32检查支持解压缩数据的限制大小功能,以防止内存在解压缩过程中被恶意破坏支持软件来停止解压过程

图像引擎

- 二维图形引擎(RGA):

- 源格式: ABGR8888,XBGR888,ARGB8888,XRGB888 RGB888,RGB565 RGBA5551,RGBA4444 YUV420平面,YUV420半平面 YUV422平面,YUV422半平面 YUV 10位为YUV420/422半平面 BPP8,BPP4,BPP2,BPP1

- 目标格式: ABGR8888,XBGR888,ARGB8888,XRGB888 RGB888,RGB565RGBA5551,RGBA4444 YUV420平面,YUV420半平面 YUV422平面,YUV422半平面

- 像素格式转换,BT.601/BT.709

- 最大分辨率: 8192x8192输入,4096x4096输出

- BitBLT(bit block transfer,位块传送,位图数据块的传送) 两个源BitBLT: A+B=B仅BitBLT,在B固定时,A支持旋转和缩放, A+B=C第二个源(B)有相同的属性与(C)+旋转功能

- 颜色填充为渐变填充和图案填充

- 高性能的拉伸和收缩性能

- 用于文本渲染的单色扩展

- 新的综合每像素alpha(颜色/alpha通道分开)

- Alpha混合模式包括Java 2波特-达夫合成混合规则,色度键,模式掩模,衰落

- 分散操作

- 0、90、180、270度旋转

- x镜、y镜和旋转操作

- 图像增强处理器(IEP):

- 图像形式 输入数据: YUV420/YUV422,半平面/平面,UV交换 输出数据: YUV420/YUV422,半平面,UV交换,平铺模式 YUV下采样转换从422到420 最大分辨率的动态图像高达1920x1080

- De-interlace 反交错

显示交互

- 一个最多为24位的RGB并行视频输出接口

- 一个BT.1120个视频输出接口

- 一个4车通道的MIPI DSI接口,每车通道高达1Gbps

- 最高1080p@60fps

视频输出处理器(VOP)

- 高达1920x1080 @60fps

- Multiple layer 多层处理

- 背景层

- Win0层

- Win2层

- 输入格式:RGB888、ARGB888、RGB565、YCbCr422、YCbCr420、YCbCr444

- 1/8到8的缩小和放大引擎

- 支持虚拟显示

- 256级alpha混合(预乘alpha支持)

- 透明颜色键

- YCbCr2RGB (rec601-mpeg/ rec601-jpeg/rec709)

RGB2YCbCr (BT.601/BT.709)支持多区域Win0层和Win2层可互换叠加- 支持RGB或YUV域覆盖

- BCSH(亮度、对比度、饱和度、色调调节)

- BCSH: YCbCr2RGB (rec601-mpeg/ rec601-jpeg/rec709)

- BCSH: RGB2YCbCr (BT.601/BT.709)

- 支持伽马调节

- 支持抖动下降快板RGB888 to 666、RGB888 to 565和抖动下降FRC(可配置)RGB888 to 666

- 空白和黑色显示

声频接口

- 8个通道的I2S0,

- 最多8个通道TX和8个通道RX路径

- 音频分辨率从16位到32位

- 采样率高达192 KHz

- 提供主从工作模式,软件可配置

- 支持3种I2S格式(正常、左对齐、右对齐)

- 支持4种PCM格式(PCM:脉冲编码调制,是将模拟信号转化为数字信号的一种方法)(early, late1, late2, late3)

- I2S模式和PCM模式不能同时使用

- 2个通道的I2S1/I2S2(用于单向传输音乐,效率高)

- 多达2通道的TX和2通道的RX路径

- 音频分辨率从16位到32位

- 采样率高达192 KHz

- 提供主从工作模式,软件可配置

- 支持3种I2S格式(正常、左对齐、右对齐)

- 支持4种PCM格式(PCM:脉冲编码调制,是将模拟信号转化为数字信号的一种方法)(early, late1, late2, late3)

- I2S和PCM不能同时使用

- PDM(pulse-duration modulation:脉冲宽度调制,多用传输麦克风录音)

- 最多8个通道

- 音频分辨率从16位到24位

- 采样率高达192 KHz

- 支持PDM主接收模式

- TDM(Time Division Multiplex:时分多路转换,多用于双向音频通讯)

- 支持最多8个通道的TX和8个通道的RX路径

- 音频分辨率从16位到32位

- 采样率高达192 KHz

- 提供主从工作模式,软件可配置

- 支持3种I2S格式(正常、左对齐、右对齐)

- 支持4种PCM格式(early, late1, late2, late3)

- 音频PWM

- 支持将PCM转换为PWM格式

- 采样率高达16倍

- 支持2x/4x/8x/16过采样的线性插值

- 支持11位可屏蔽的L/R通道PWM输出

- 数字音频编解码器

- 支持3通道数字ADC

- 支持2通道数字DAC

- 支持I2S/PCM接口

- 支持I2S/PCM主从模式

- 支持在I2S模式下的4通道音频输出

- 支持在I2S模式下的2通道音频接收

- 支持在PCM模式下的2通道音频传输或接收

- 支持数字ADC和数字DAC的16~24位样本分辨率

- 数字ADC和数字DAC都支持三组采样率。第0组是8khz/16khz/32kHz/64kHz/128khz,第1组是11.025khz/22.05khz/44.1khz/88.2khz/176.4khz,第2组是12khz/24khz/48khz/96khz/192khz

- 数字ADC滤波器的通频带为0.45625*fs

- 支持+/-0.1dB范围内的数字ADC通带纹波

- 数字ADC滤波器的停止频带为0.5*fs

- 支持数字ADC阻带衰减至少60dB

- 支持数字ADC和数字DAC的音量控制

- 支持自动电平控制(ALC)和数字ADC噪声门

- 支持通过I2C总线与模拟编解码器通信

连接

- SDIO接口

- 兼容SDIO3.0协议

- 4位数据总线宽度

- GMAC 10/100/1000M以太网控制器

- 使用RGMII接口,支持10/100/1000-Mbps的数据传输速率

- 使用RMII接口,支持10/100-Mbps的数据传输速率

- 同时支持全双工和半双工的操作

- 支持TCP分段卸载(TSO)和UDP分段卸载(USO)网络加速

- USB 2.0 Host(主机)

- 兼容USB 2.0规范

- 支持高速(480Mbps)、全速(12Mbps)和低速(1.5Mbps)模式

- 支持增强的主机控制器接口规范(EHCI),版本1.0

- 支持开放主机控制器接口规范(OHCI),版本1.0a

- USB 2.0 OTG (一键拷贝)

- 兼容规范: 通用串行总线规范,修订版2.0 通用串行总线(xHCI)的可扩展主机控制器接口,修订版1.1

- 支持控制、批量、中断、同步传输

- SPI接口

- 支持2个SPI控制器,支持两个芯片选择输出

- 支持串行从属模式和串行从属模式,软件可配置

- I2C接口

- 支持6个I2C接口(I2C0-I2C5)

- 支持7位和10位的地址模式

- 软件可编程时钟频率

- 在标准模式下,I2C总线上的数据可以以100K bits/s的速率传输,在快速模式下高达400K bits/s,在快速模式Plus下以1m bits/s的速率传输\

- UART接口

- 支持6个UART接口(UART0-UART5)

- 支持5位、6位、7位、8位串行数据的传输或接收

- 标准的异步通信位,如启动、停止和奇偶校验

- 支持不同的UART操作输入时钟,波特率高达4Mbps

- 支持自动流量控制模式(UART2除外)

其他

- 多组GPIO

- 所有的gpos都可以用来生成中断

- 支持电平触发和边缘触发中断

- 支持可配置极性电平触发中断

- 支持可配置的上升沿、下降沿和双沿触发中断

- 支持可配置的拉方向(弱上拉和弱下拉)

- 支持可配置的驱动强度

- 温度传感器(TS-ADC)

- 支持用户自定义模式和自动模式

- 在用户定义模式下,启动转换可以完全由软件控制,也可以由硬件生成。

- 在自动模式下,可以配置报警(高低温度)中断的温度

- 在自动模式下,系统复位的温度可进行配置

- 支持2通道TS-ADC(分别用于CPU和NPU),每个通道的温度标准都可以配置

- -40~125°C温度范围和5°C温度分辨率

- 12位SARADC高达732 S/ S的采样率

- 逐次逼近ADC

- 10位分辨率

- 高达1MS/s的采样率

- 6个单端输入通道

- OTP

- 支持32Kbit空间和更高的4k地址空间的不安全部分。

支持在安全模型中读取和编程字掩码。支持程序长度,从1位到32位。仅支持8位读操作可读程序和读状态程序故障地址记录

- 封装类型

- FCCSP 409-pin(主体:14mm x 14mm;锡球的尺寸:0.3mm;球距:0.65mm)

大概价格区别

RV1109:54

RV1126:69

RK809-2:8

1GB DDR4 K4A8G165WA-BCTD:12

2GB DDR4 K4AAG165WA-BCTD :31

8GB EMMC KLM8G1GETF-B041:12

电路设计

复位功能

RV11XX硬件复位通过nPOR引脚来实现,低电平有效,为保证芯片稳定工作,所需的最短复位时间为 100个24MHz时钟周期,即至少4.17us以上。

建议复位信号并联100nF电容,靠近芯片引脚放置,增强抗干扰能力,防止误触发导致系统复位。 nPOR引脚所在的IO电源域的电平要保持跟RESET引脚的上拉电平一致。如图1-1,1-2所示。

图 1-1 RV11XX芯片复位引脚

图 1-2 RK809-2复位引脚

系统启动引导顺序

RV11XX系统允许多种启动引导方式,在系统复位后,芯片内部集成的启动代码会按如下顺序进行自动判断引导:

- SPI FLASH

- Nand FALSH

- EMMC FLASH

- SDMMC CARD

- USB OTG

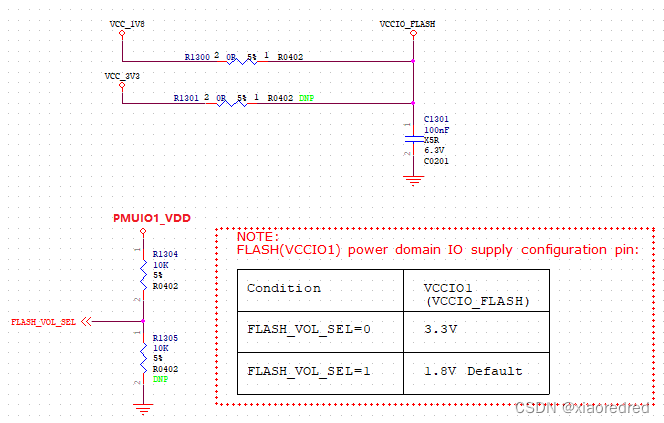

**系统初始化配置信号 **

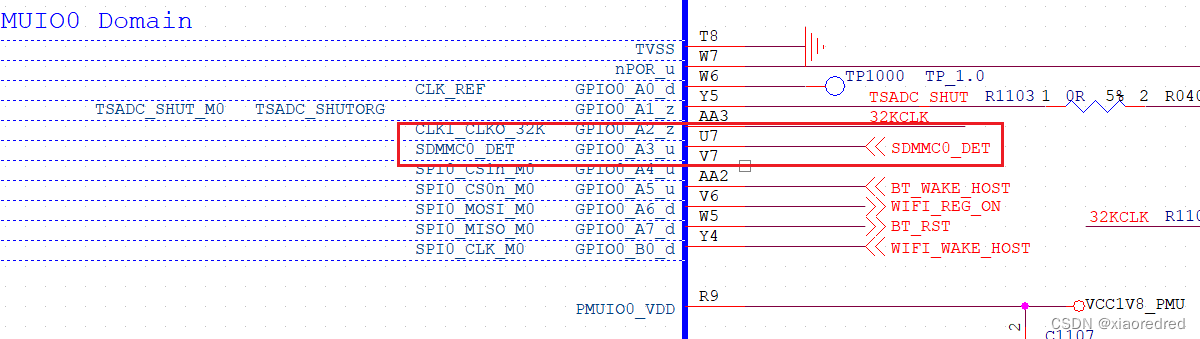

RV11XX中有两个信号会影响系统的启动配置,分别是PIN Y8 FLASH_VOL_SEL及PIN U7 SDMMC0_DET。在系统复位释放时,芯片会根据两引脚的输入电平配置相应模块的开机默认功能。

PIN Y8 FLASH_VOL_SEL用来配置存储接口IO的VCCIO1_VDD电源域电平,以保证电平与启动代码的配置相匹配。如果外部存储接口的IO电平是1.8V,则此引脚在复位期间须保持为高电平;反之存储接口 的IO电平是3.3V,则此引脚在复位期间须保持为低电平,如图1-3所示的配置。 PIN Y8的开机电平状态要求务必与存储接口的实际供电相匹配,以免造成系统稳定性风险。

图 1–3 FLASH_VOL_SEL 功能

PIN U7 SDMMC0_DET用来配置系统启动时的默认功能,当检测为高时,切换为JTAG功能,当检测为低(正常SD卡的插入状态)时,切换为SDMMC功能。此功能主要考虑带SD卡功能的机器装整机后,可以在不拆机状态下方便地进行系统底层调试。

图 1–4 SDMMC0/DEBUG复用控制管脚

Pin T8 TVSS 引脚状态决定RV11XX的模式,0接地为正常功能模式,1为测试模式。管脚的配置方式如下表所示:

表 1–1系统初始化配置信号描述

信号名内部上下拉描述FLASH_VOL_SEL下拉

FLASH(VCCIO1)电源域电平配置管脚:

0:IO电平模式为3.3V;

1:IO电平模式为1.8V;

SDMMC0_DET上拉

JTAG管脚复用选择控制信号:

0:识别为SD卡插入,SDMMC/JATG/UART管脚复用为

SDMMC输出;

1:未识别为SD卡插入,SDMMC/JATG/UART管脚复用为

JTAG功能;

TVSSNA

功能模式和测试模式选择:

0:功能模式,连接到GND;

1:测试模式。

**JTAG Debug **电路

RV11XX芯片的A7_JTAG接口符合IEEE1149.1标准,PC可通过SWD模式(两线模式)连接DSTREAM仿真器,调试芯片内部的ARM Core。RV11XX芯片的MCU_JTAG符合IEEE1149.1标准,PC可通过四线模式,调试芯片内部的MCU。

如上小节所述,PIN U7 SDMMC0_DET引脚为高时(默认为高),系统启动时默认切为A7_JTAG功能。JTAG-A7功能对应的引脚为:

表 1–2 JTAG Debug接口信号引脚信号名描述V13

A7_JTAG_TCK_M0

Cortex-A7 JTAG接口时钟输入/SWD接口时钟输入U13

A7_JTAG_TMS_M0

Cortex-A7 JTAG接口TMS输入/SWD接口数据输出W13

MCU_JTAG_TRSTn

单片机JTAG复位信号V13

MCU_JTAG_TCK

单片机JTAG接口TCK输入U13

MCU_JTAG_TMS

单片机JTAG模式选择输入信号AA13

MCU_JTAG_TDO

单片机JTAG接口数据输出Y13

MCU_JTAG_TDI

单片机JTAG接口数据输入

A7-JATG也复用在VCCIO5电源域,命名为A7-JTAG_M1,而且A7-JTAG_M1接口跟UART2_M1接口复用,默认的功能是UART2功能。如果把UART2_RX_M1持续拉低一段时间,可以切换到切到A7-JTAG功能。

表 1–3 A7-JTAG-M1接口信号

引脚信号名描述

G18

A7_JTAG_TCK_M1/UART2_TX_M1

Cortex-A7 JTAG接口时钟输入/SWD接口时钟输入

H16

A7_JTAG_TMS_M1/UART2_RX_M1

Cortex-A7 JTAG接口TMS输入/SWD接口数据输出

注意!!!

MCU_JTAG_TCK与A7_JTAG_TCKM0复用同一个引脚V13,默认为A7_JTAG_TCK*M0功能。 *

MCU_JTAG_TMS与A7_JTAG_TMSM0复用同一个引脚U13,默认A7_JTAG_TMS*M0功能。 所以如果需要A7-JTAG功能,请使用这两个引脚。 *

JTAG连接方式及标准连接器管脚定义如下图所示:

图 1–5 JTAG连接方式

电源

系统电源介绍

- PLL的供电:PLL_AVDD_0V8、PLL_AVDD_1V8

- OSC的供电:PMUIO_VDD_0V8、PLL_AVDD_1V8

- ARM供电:ARM_VDD

- LOGIC供电:LOGIC_VDD

- NPU供电:NPU_VDD

- Encode供电:VEPU_VDD

- DDR供电: VCC_DDR

- PMU GPIO:PMUIO_VDD_0V8、PMUIO_VDD_1V8、PMUIO0_VDD、PMUIO1_VDD

- ADC供电:ADC_AVDD_1V8

- USB供电:USB_AVDD_0V8、USB_AVDD_1V8、USB_AVDD_3V3

- MIPI DSI供电:MIPI_DSI_TX0_AVDD_0V8、MIPI_DSI_TX0_AVDD_1V8

- MIPI CSI供电:MIPI_CSI_RX0_AVDD_0V8、MIPI_CSI_RX1_AVDD_0V8、

- MIPI_CSI_RX0_AVDD_1V8、MIPI_CSI_RX1_AVDD_0V8

- VCCIO供电:VCCIO_VDD_1V8,

- VCCIO1_VDD/VCCIO2_VDD/VCCIO3_VDD/VCCIO4_VDD/VCCIO5_VDD/VCCIO6_VDD/

- VCCIO7_VDD

上电时序介

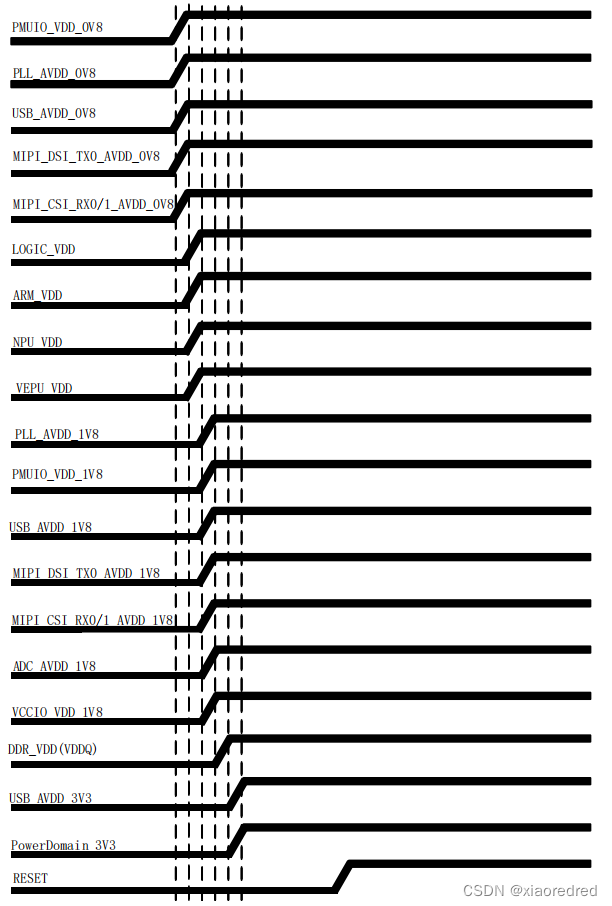

上电时序要求如图1-6所示:

图 1–6上电时序

上电时序说明如下:

数字VDD需要按照如下的顺序上电:

PMUIO_VDD_0V8/PLL_AVDD_0V8 **→ **LOGIC_VDD/ARM_VDD/NPU_VDD/VEPU_VDD (注意:ARM_VDD/NPU_VDD/VEPU_VDD 的上电时序可以比LOGIC_VDD早,也可以比

LOGIC_VDD晚)

USB 上电说明

USB_AVDD_0V8 **→ **USB_AVDD_1V8 **→ **USB_AVDD_3V3

三个上电时序的时间间隔Td>0us即可以。MIPI DSI/CSI

MIPI_DSI_TX0_AVDD_0V8/ MIPI_CSI_RX0_AVDD_0V8/MIPI_CSI_RX1_AVDD_0V8→

MIPI_DSI_TX0_AVDD_1V8/ MIPI_CSI_RX0_AVDD_1V8/MIPI_CSI_RX1_AVDD_1V8

时间间隔Td>0us。

DDR PHY

LOGIC_VDD **→ **PLL_AVDD_1V8 **→ **VCC_DDR(VDDQ) (注意:VDDQ(VCC_DDR)跟PLL_AVDD_1V8同时上电,或者比PLL_AVDD_1V8晚上电

都可以。)

GPIO Power on

PMUIO_VDD_0V8 **→ **LOGIC_VDD **→ **PMUIO_VDD_1V8/VCCIO_VDD_1V8 **→ **PMUIO0_VDD/PMUIO1_VDD/VCCIO1_VDD/VCCIO2_VDD/VCCIO3_VDD/VCCIO4_VDD/VCCIO5_VDD/VCCIO6_VDD/ VCCIO7_VDD

总结

上电时序遵循:

0.8V(最小系统所有的0.8V电源)

**→** LOGIC_VDD/ARM_VDD/NPU_VDD/VEPU_VDD

** →**1.8V(最小系统所有的1.8V)

**→ **VCC_DDR

** → **3.3V(最小系统的所有3.3V)

时序的时间间隔Td>0us。

一般都是先低压再高压,如0.8 **→ **1.8

**→ **3.3

先 电源管理模块 / 锁相环 / USB / MIPI _**0V8** **→ **内核(逻辑单元/ARM/NPU/VEPU)

**→ **锁相环 / 电源管理模块 / USB /MIPI / ADC / IO _**1V8** **→ DDR** **→ **USB / PowerDomain _**3V3** / **复位**

芯片电源管理(PMUIO)接口介绍

** **如果RV11XX的某些产品方案需要实现不断电待机的功能,那么可以通过RV11XX的电源管理 (PMUIO)模块来实现。在PMUIO电源域,可以通过接收按键信号或者上升沿信号对其他的功能模块的电源进行上下电控制,也可以接收外设输出的唤醒信号,从而实现产品的待机和唤醒的功能。

- PMUIO模块的供电管脚 PMUIO0_VDD、PMUIO1_VDD、PMUIO_VDD_0V8和 PMUIO_VDD_1V8 常供电。

- PMUIO0_VDD和PMUIO1_VDD分别表示各自电源域的IO电平,可以连接1.8V或者3.3V。

- pinW7为nPOR为系统的复位引脚(如上复位功能小节所述),低电平有效。

- Pin W10为 PMIC_INT功能,可以接收PMIC回传的中断信息。

- Pin Y10为PMIC_SLEEP功能,此管脚用于控制需要断电的模块的电源。系统进入待机状态 时,此管脚会输出高电平的休眠指示信号,根据软件dts文件的配置,部份电源会关闭,部分 电源会调低电压。当系统被唤醒时,PMIC_SLEEP恢复低电平输出状态,恢复各路电源输出。

- Pin Y5为TSADC_SHUT功能,此管脚可用于控制nPOR,可以通过一个0R电阻连接到RESET。芯片温度超出所设置的温度时,此管脚可以输出低电平信号,对RV11XX和RK809-2进行复位、控制电源下电并重新上电,在寄存器清零的同时复位整个系统。

**芯片不断电待机方案 **

RV11XX系统电源采用低功耗设计,待机状态下可分为不掉电供电区和待机掉电区,两部分独立供电,如图所示。

图 1–6待机电路方案

待机状态下保留如下四组电源不关断:

- DDR:VCC_DDR,为DDR自刷新提供电源;

- PMU:PMUIO0_VDD、PMUIO1_VDD、 PMUIO_VDD_0V8和PMUIO_VDD_1V8,提供对应PMUIO电源域的IO供电及PMU内部硬件逻辑供电;

- PLL:PLL_AVDD_0V8、PLL_AVDD_1V8,为PLL及OSC工作提供电源;

- LOGIC_VDD不掉电。

注意!!!

*如果应用上,在待机时有任何一组VCCIO不断电,那么VCCIO_VDD_1V8也不能断电。 *

官方推荐电源管理芯片介绍

RK809-2

RK809-2****特征

电源输入范围:2.7V-5.5V

具有两个独立的电池电压和电流ADC的精准电量计

内置实时时钟(RTC)

16uA的极低待机电流(在32KHz时钟频率下)

实地输出的耳机驱动

不含滤波电感的1.3W Class D类功放

固定及可编程可选择的电源启动时序控制

内置高性能音频编解码器

内置独立PLL 支持麦克风输入 DAC和ADC都支持I2S数字输入 支持ALC,限幅器和噪声门 支持可编程的数字与模拟增益 支持16bits-32bits的比特率 采样率高达192kHz 软件支持master和slave两种工作模式配置 支持3种I2S格式(标准,左对齐,右对齐) 支持PDM模式(外部输入PCLK)电源通道:

通道1:同步降压DC-DC转换器,2.5A max 通道2:同步降压DC-DC转换器,2.5A max 通道3:同步降压DC-DC转换器,1.5A max 通道4:同步降压DC-DC转换器,1.5A max 通道5:同步降压DC-DC转换器,2.5A max 通道6-7、9-14:低压差线性稳压器,500mA max 通道8:低噪声、高电源抑制比的低压差线性稳压器,100mA max 通道15:开关,3A max 通道16:开关,1.5A max封装:7mmx7mm QFN68

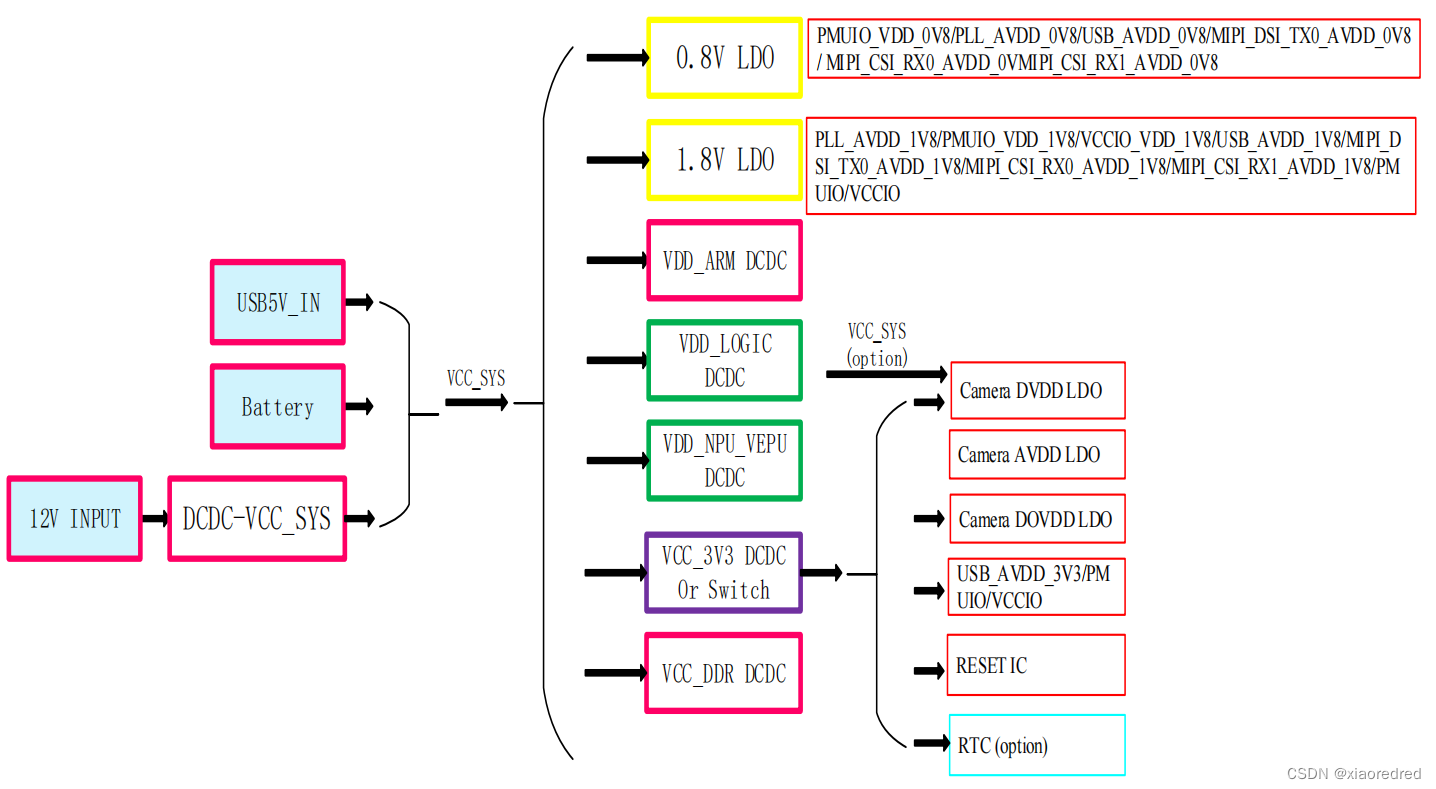

RV11XX+RK809-2 电源树

RK809-2****注意事项

32.768晶体的匹配电容推荐值为22pF,用户可根据所用晶体的具体规格微调此参数;

* 注意:**为了降低功耗**PMIC RTC**的晶体振荡都做的比较弱,在**XOUT**或**XIN**的管脚上用普通的示波器是测不到振荡信号的,或示波器探头一碰上去就会停**振,要测**32.768k**信号请测试**CLK32K**管脚。*VCC_RTC必须第一个供电,且其电压数值必须是供给RK809-2的输入电源中最高的。

BUCK1,BUCK2的输出电容必须大于30uF以上才能保证有比较好的去耦效果,特别是大电流 高动态的负载情况下,可以适当加大输出去耦电容;

RK809-2自带USB OTG供电功能,有短路保护功能,可配置1.0-1.5A的输出限流;

直接由输入电源控制的开机逻辑如下:当存在电源输入时,初级DCDC降压输出VCC5V0_SYS和VCC_RTC,电源通过外部分压电路后输入到VDC的电平大于0.55V,此时PMIC开始工作、输出电压;

通过按键控制的开关机逻辑如下:PWRON脚内置上拉电阻,上拉到VCCRTC,当检测到低电平时间超过500ms就会自动开机;开机后如果PWRON脚被拉低超过6s就会强制关机(通常用于系统死机后的强制关机,再开机);在休眠以及唤醒操作时,PWRON脚的低电平需维持20ms以上

RK809-2工作的基本条件: - VCC_RTC供电; - VCC5V0_SYS供电; - 检测到了如下三种情况之中的一种,RK809-2自动开机:PWRON脚为低电平并维持 500mS;VDC电平超过0.55V;内部RTC Alarm开机使能且定时时间到。- 开启上电流程,每个时序间隔是2mS,上面一个时序电压输出符合要求后才会继续下一个 时序,直到所有时序上电结束,并释放reset,完成上电流程; - RK809-2检测到如下两种情况之一,会自动关机: - I2C写DEVICE_OFF=1; - PWRON脚为低超过6s。 - RK809-2开始下电流程后,会在1个RTC时钟周期后(约30.5us后)拉低reset,再经过2ms以后同时关断所有电源输出,完成下电流程;

RK809-2检测到如下两种情况之一,会自动关机: - VCC_RTC供电;- I2C写DEVICE_OFF=1; - PWRON脚为低超过6s。

RK809-2开始下电流程后,会在1个RTC时钟周期后(约30.5us后)拉低reset,再经过2ms以后同时关断所有电源输出,完成下电流程;

RK809-2具体设计说明,请参考RK PMIC相关设计文档《AN_RK809_V1.1_20200310 》。

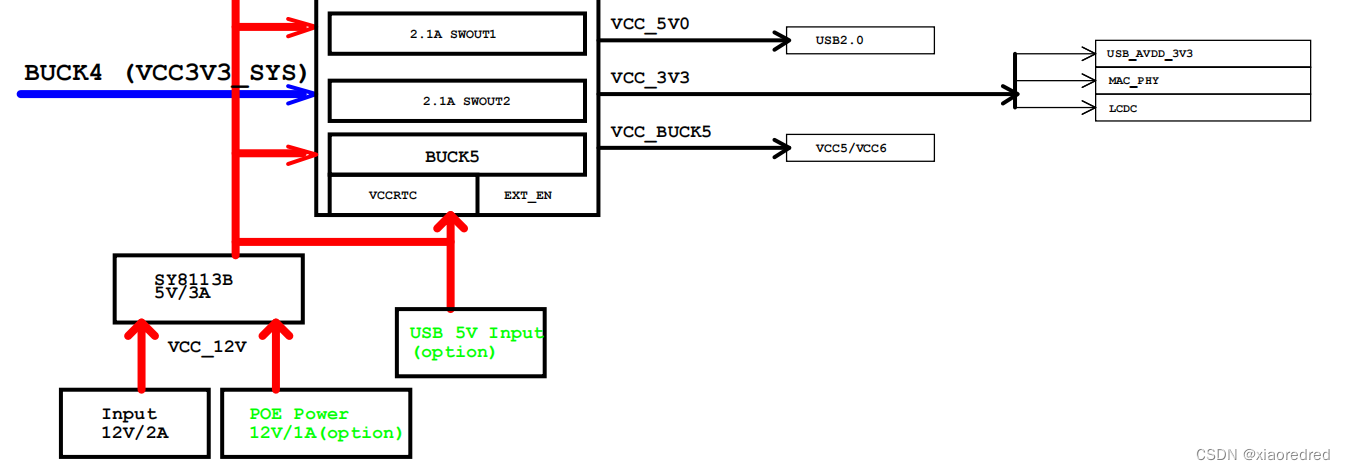

分立元器件搭建电源

有的产品方案会用到分立电源方案,有且不仅有以下几个原因:

- PCB空间有限,不适合放置PMIC。

- 功能相对简单,需要的电源相对简单。

- 需要做快速启动的方案。

分立电源

电源说明:

- 对于不同的产品类型总的输入电源是有区别的,UVC方案用到USB5V输入,电池方案会直接 使用电池输入,标准IPC方案12V输入要增加一个DCDC转换成低压。

- 对于绿框内的电源,VDD_LOGIC、VDD_NPU、VDD_VEPU在不同的方案中可能会有合并的设计。 a) 在UVC方案中,NPU和VEPU可能会合并供电,这路电源电压会按照NPU的频率电压表 配置,那么带来的影响就是当NPU跑重载的时候,电压会高于VEPU所需的电压,从而增加了 VEPU的运行功耗。具体可以参看UVC的图纸。b) 对于标准IPC38X38的板子,由于主板面积的限制,那么就需要把VDD_LOGIC、 VDD_NPU、VDD_VEPU三路电源合并,合并后这路电源就不能调压了,需固定一个相对高 一点的电压以满足NPU和VEPU的电压需求。带来的影响就是导致LOGIC的运行功耗会增 加, RV1126NPU的性能会受到限制,不能跑到最高的算力。具体可以参看38X38IPC的图 纸。 c)对于电池IPC方案,这3路电源独立,不合并,主要原因是运行功耗的优势要放在第一位置。具体可以参看电池IPC的图纸。

- 需要用到分立的RESET IC,注意RESET IC的选型,保证RESET 信号的电平跟PMUIO0_VDD一致。

- 是否需要RTC芯片,取决于产品功能需求,如果不需要,那么可以删除。

电源原理图设计

LOGIC,ARM,NPU,VEPU,PLL,DDR的电容容值及数量,要求完全参照参考设计。

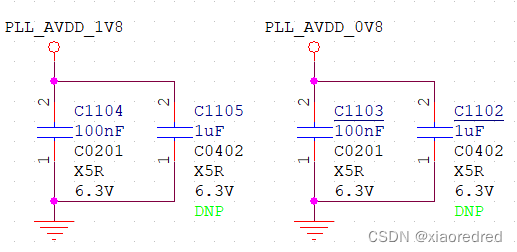

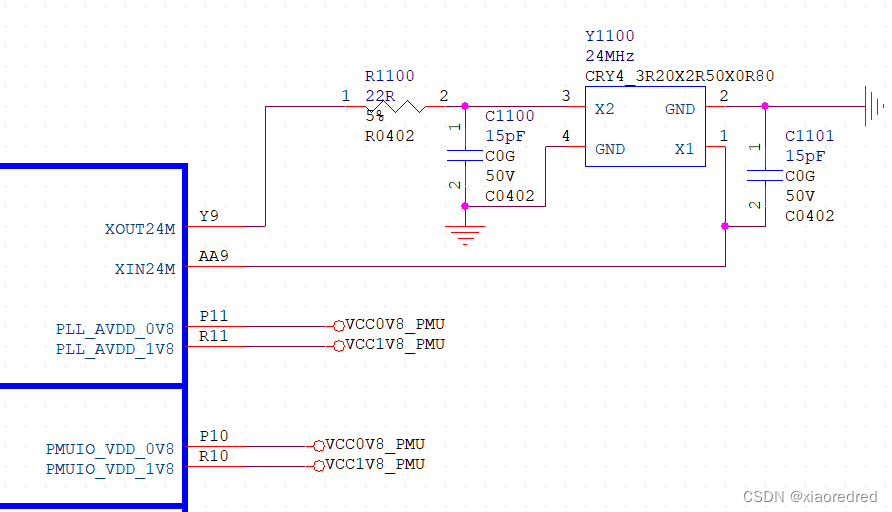

**PLL电源设计 **

**RV11XX芯片PLL电源:**

电源待机状态PLL

PLL_AVDD_0V8,PLL_AVDD_1V8

不可关断电源

PLL的电源有两个,分别是PLL_AVDD_0V8和PLL_AVDD_1V8,设计上必须使用去耦电容,并靠近管脚的位置摆放。电源上建议使用LDO为PLL单独供电,特别是DDR工作频率较高时,稳定的PLL电源有助于提高SOC的工作稳定性,注意去耦电容应靠近管脚摆放。电源纹波要求VPP<10%。

ARM电源设计

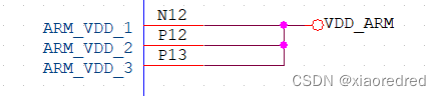

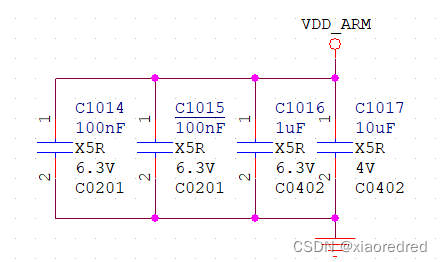

RV11XX ARM电源的典型值为0.8V,实际电压根据SDK动态调压参数控制,频率越高电压越高,根据参考设计来设计,不建议跟其他的电源合并。电源芯片选型要求其供电能力不小于1A。请不要删减参考原理图中的电容。Layout时将大电容尽可能放置在RV11XX芯片背面(单面贴时请靠近芯片放置),电源纹波要求VPP<10%,电容如下图所示:

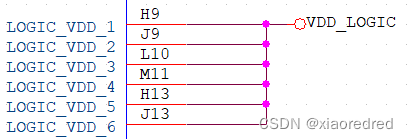

LOGIC电源设计

RV11XX LOGIC电源的典型值为0.8V,不允许动态调压,不建议跟其他电源合并,请按照参考图设计。电源芯片选型要求其供电能力不小于2A。请不要删减参考原理图中的电容。Layout时请将大电容放置在RV11XX芯片背面(单面贴时请靠近芯片放置),电源纹波要求VPP<10%,电容如下图所示:

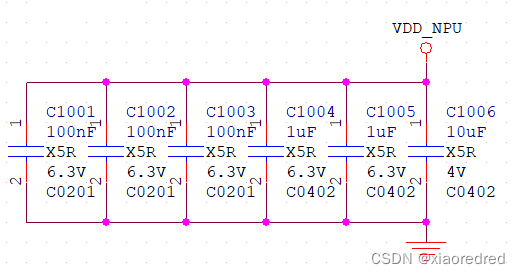

NPU****电源设计

RV11XX NPU电源的典型值为0.8V,实际电压根据SDK动态调压参数控制,可以根据实际产品情况,NPU和VEPU电源合并。NPU电源芯片选型要求其供电能力不小于2A.请不要删减参考原理图中的电容。Layout时请将大电容放置在RV11XX芯片背面(单面贴时请靠近芯片放置),电源纹波要求VPP<10%,电容如下图所示:

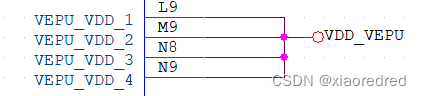

VEPU****电源设

RV11XX VEPU电源的典型值为0.8V,实际电压根据SDK动态调压参数控制, 可以根据实际产品情况,NPU和VEPU电源合并。VEPU电源芯片选型要求其供电能力不小于1.0A.请不要删减参考原理图中的电容。Layout时请将大电容放置在RV11XX芯片背面(单面贴时请靠近芯片放置),避免大负载情况下引起电源纹波偏大,电源纹波要求VPP<10%,电容如下图所示:

**动态调压 **

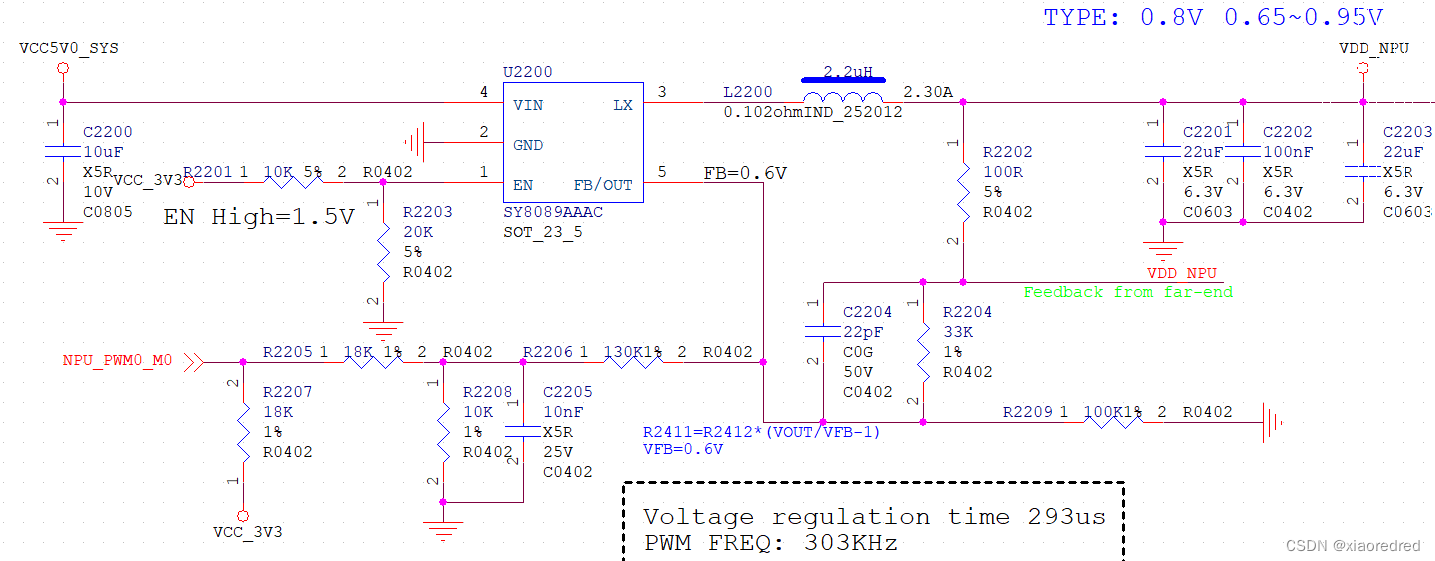

RX11XX的ARM/NPU/VEPU电源增加动态调压的功能,实现方法如下:

- 如果由RK809-2供电,动态调压可由PMIC来完成;

- 如果ARM、NPU和VEPU由分立电源供电,动态调压可以通过PWM波形输出管脚,经过RC 滤波后输出0~3.3V不同的电压的直流电平,该直流电平经过电阻网络叠加到DCDC的反馈电 压输入处,实现DC-DC输出电压的调节。通过RV11XX相关的寄存器可以改变PWM的频率和 占空比,最终可以实现动态调节DC-DC的输出电压。

设计中需要注意事项如下:

- VCC_3V3电源的直流电压值误差不要超过±50mV。

- 计算出来是参考值,实际阻值可以在计算值的左右波动,尽量接近。

- 所有电阻的精度均要求1%。

- 要求选用的DC-DC参考电压Vref 0.6V,DCDC的Vref精度偏差不能超过2%。

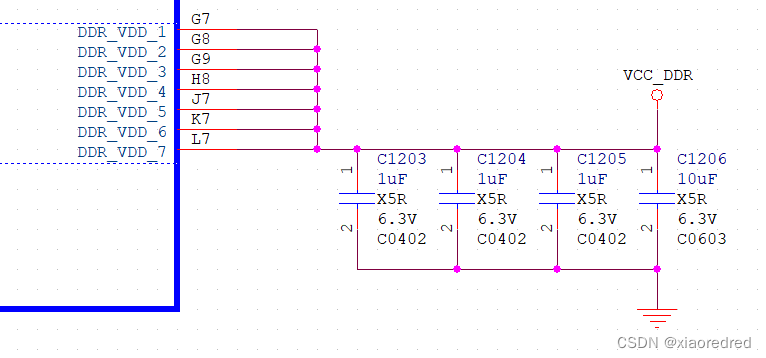

DDR****电源设计

RV11XX芯片的DDR控制器接口支持DDR3/DDR3L/DDR4/LPDDR3/LPDDR4。

DDR3典型电压值为1.5V,DDR3L典型电压值为1.35V,LPDDR3典型电压值为1.2V,DDR4 典型电压值为1.2V,LPDDR4典型电压值为1.1V。DDR颗粒的电源要求与RV11XX的DDR IO 电源采用同一电源网络。请不要删减参考原理图中的电容。

RV11XX的DDR控制器内部集成Vref电路,可以给控制器或颗粒供应VREF电压。应用中根据 不同颗粒运行的不同状态,软件驱动上会动态调整VREF电压值。每个参考电源管脚旁放置 一个1nF的去耦电容。

Vref_CA由VCC_DDR通过分压电阻产生,电阻精度要求1%。

电源纹波要求在±5%。

举例:LPDDR3 SDRAM端的Vref_CA可由电阻分压电路产生,其中Vref_CA=VCC_DDR/2,而Vref_DQ则需要根据ODT策略来调整,可以根据驱动强度和ODT值调整对应的Vref电压。 800MHz频率下,芯片端的驱动强度为34.3ohm,SDRAM端ODT为240ohm,因此ODT enable时,根据公式算出来的SDRAM Vref=0.56*VCC_DDR。这个电压可以由Pin M6直接提供。

注意!!!

*关于不同颗粒Vref_DQ的设计: *

DDR4 Vref_DQ可以通过组件内的软件进行调整,DDR3/DDR3L的ODT功能enable时内部会同时上下拉,**Vref_DQ=Vref_CA=VCC_DDR/2;LPDDR4没有Vref 电压;所以只有LPDDR3需要单独调节Vref_DQ。

GPIO****电源设计

在RV11XX中,GPIO类型为1.8V/3.3V可配置。

RV11XX中,有两种类型的GPIO,其中一种类型的GPIO提供4档驱动强度可调,另一种类型 的GPIO提供16档驱动强度可调。根据GPIO的类型不同,初始默认驱动强度也不同,请参考芯片TRM进行配置修改,也可以参考《RV1126_RV1109_PINOUT_EN》文档中表3“Pin Control Registers”和表4“Pin Default Status”。

- IO电源管脚名,如VCCIO1_VDD表示,VCCIO1电源域的电平,支持3.3V/1.8V。其他的IO电 源管脚名分别为:VCCIO2_VDD,VCCIO3_VDD,VCCIO4_VDD,VCCIO5_VDD,VCCIO6_VDD,VCCIO7_VDD。

- VCCIO1/2/3/4/5/6/7_VDD可以支持3.3V/1.8V。

- VCCIO_VDD_1V8是VCCIO1/2/3/4/5/6/7电源域的公共电源,只要用到VCCIO1~VCCIO7电源 域的GPIO,这个引脚必须供电。

- PMUIO0电源域的IO电平(管脚名 PMUIO0_VDD):支持3.3V/1.8V。

- PMUIO1电源域的IO电平(管脚名 PMUIO1_VDD):支持3.3V/1.8V。

- PMUIO_VDD_1V8是PMUIO0和PMUIO1电源域的公共电源,必须供电1.8V。

- PMUIO0_VDD_0V8是PMUIO和PMUIO1电源域的公共电源,必须供电0.8V。

- 建议电源域的每个供电管脚上放置一个100nF去耦电容,并靠近供电管脚摆放。详细设计请 参考RV11XX芯片参考原理图。

- 主控电源域的IO电平要与对接外设芯片的IO电平保持一致**,还要注意软件的电压配置要跟硬件的电压一致,否则可能会导致GPIO的损****坏。 **

- 电源纹波要求在±5%。

注意!!!

*关于GPIO电源域IO电平匹配问题: *

GPIO的电源域PMUIO0_VDD,PMUIO1_VDD,VCCIO1_VDD,VCCIO2_VDD,VCCIO3_VDD,VCCIO4_VDD,VCCIO5_VDD,VCCIO6_VDD,VCCIO7_VDD,这些电源的电压要跟所接的外设的IO电平的电压保持一致,否则可能会导 **致GPIO的损坏。 *还要注意软件的电压配置要跟硬件的电压一致:比如硬件IO电平接1.8V,软件的电压配置也要相应的配成1.8V;硬件IO**电平接3.3V,软件的电压配置也要用3.3V,否则也可能会导致GPIO的损坏。*

**电源峰值电流表 **

下表为RV11XX峰值电流评估结果,仅供参考。测试条件如下:

电源

最小(V)

典型V(V)

最大(V)

电流(mA)

备注

ARM_VDD

TBD0.8TBD730

LOGIC_VDD

TBD0.8TBD1750

VEPU_VDD

TBD0.8TBD770

NPU_VDD

TBD0.8TBD1340

DDR_VDD

TBDTBDTBDTBD

取决了DDR颗粒类型

电路PCB设计

控下方ARM滤波电容组合:10uF+1uF+100nF*2

主控下方NPU滤波电容组合:10uF+1uF2+100nF3

主控下方VEPU滤波电容组合:10uF+1uF+100nF*2

主控下方LOGIC滤波电容组合:10uF+1uF2+100nF2

主控下方DDRIO滤波电容组合:10uF+1uF*3+100nF,请保持跟参考设计一样。其他位置的电 容容值和数量和布局有差异。

滤波电容的位置可以参考官方发布的《RV1126_RV1109_Template》。 PLL电源设计: PLL的滤波电容摆放在PLL电源球位附近。

晶振电路****设计

晶振原理图设计

RV11XX芯片内部的反馈电路与外置的24MHz晶体振荡电路一起构成系统时钟电路,推荐的晶振连接方式及器件参数如下图所示。

注意!!!

选用的电容需要与晶振的负载电容匹配,材质建议采用NPO。建议选用4Pin 贴片晶振,其中2个GND管脚与地充分连接,增强系统时钟抗ESD干**扰能力。选用24MHz频偏20ppm。

系统24MHz时钟使用有源晶体时,从管脚XIN24M输入,管脚XOUT24M悬空,时钟的幅度是

1.8V±10%。时钟参数如下表所示:

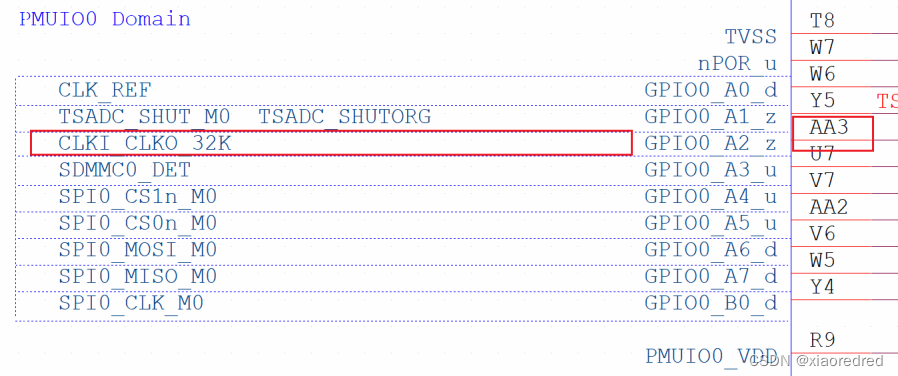

RV11XX芯片在待机时所需要的32.768KHz时钟,可以由PMU内部的PVTM提供,也可以由外部输入32.768KHz时钟。如果使用外部时钟,32.768KHz时钟信号可以从PMIC或外置RTC时钟源获取,输入到引脚pin AA3,如下图所示。

外置32.768KHz RTC时钟参数如下表所示:

晶振PCB设计

**晶体的XIN、XOUT信号走线全程做包地处理,并保证这些信号有完整的参考地,晶体电路下方不能有高速信号穿过。晶体放在主控附近。 **

版权归原作者 xiaoredred 所有, 如有侵权,请联系我们删除。