一、单选题

1.存储器是计算机系统中的记忆设备,它主要用来 ( )。

A、存放数据

B、存放程序

C、存放数据和程序

D、存放微程序

正确答案:C

2.存储周期是指( ) 。

A、存储器的读出时间

B、存储器的写入时间

C、存储器进行连续读和写操作所需的最短时间间隔

D、存储器进行连续写操作所需的最短时间间隔

正确答案:C

3.和外存储器相比,内存储器的特点是( )。

A、容量大,速度快,成本低

B、容量大,速度慢,成本高

C、容量小,速度快,成本高

D、容量小,速度快,成本低

正确答案:C

4.EPROM是指( )。

A、随机读写存储器

B、只读存储器

C、可编程的只读存储器

D、可擦可编程的只读存储器

正确答案:D

5.动态半导体存储器是( ) 。

A、DRAM

B、PROM

C、SRAM

D、ROM

正确答案:A

6.需要刷新的存储器是( ) 。

A、Cache

B、ROM

C、静态存储器

D、动态存储器

正确答案:D

7.若静态存储器中有1K个存储单元,需要的地址线数量为( )根。

A、1024

B、10

C、32

D、64

正确答案:B

8.断电后会丢失信息的是 ( ) 。

A、ROM

B、RAM

C、PROM

D、快闪存储器

正确答案:B

9.下面叙述不正确的是( ) 。

A、随机存储器可随时存取信息,掉电后信息丢失

B、在访问随机存储器时,访问时间与单元的物理位置无关

C、内存储器中存储的信息均是不可改变的

D、随机存储器和只读存储器可以统一编址

正确答案:C

10.某RAM存储器容量为32K*16位则 ( )。

A、地址线为16根,数据线为32根

B、地址线为32根,数据线为16根

C、地址线为15根,数据线为16根

D、地址线为19根,数据线为19根

正确答案:C

11.一个512KB的SRAM存储器,地址线和数据线的总和是( ) 。

A、17

B、19

C、27

D、36

正确答案:C

12.【2010统考真题】 假定用若干 2K×4位的芯片组成一个 8K×8位的存储器,则地址 0B1FH 所在芯片的最小地址是 ( )。

A、0000H

B、0600H

C、0700H

D、0800H

正确答案:D

题目解析:

8K存储器地址从0000H~1FFFH,由四个2K芯片组成,则四个2K芯片的地址范围是:

0000H~07FFH

0800H~0FFFH

1000H~17FFH

1800H~1FFFH

地址 0B1FH位于0800H~0FFFH范围

13.【2016统考真题】 某存储器容量为 64KB, 按宇节编址, 地址4000H~5FFFH为 ROM 区、 其余为 RAM 区。若采用 8Kx4 位的 SRAM 芯片进行设计, 则需要该芯片的数量是( )。

A、7

B、8

C、14

D、16

正确答案:C

题目解析:

ROM地址为4000H~5FFFH,占8K空间,剩余64K-8K=56K是RAM空间,则56K8bit/8K4bit = 14片

14.【2014统考真题】某容量为256MB的存储器由若干4M×8位的DRAM芯片构成,该DRAM芯片的地址引脚和数据引脚总数是( )。

A、19

B、22

C、30

D、36

正确答案:A

题目解析:

4M存储器的地址线有22根,但对于DRAM,地址线复用,故4M×8位的DRAM芯片地址线为11根,加上数据8位,共计19根

15.【2012统考真题】下列关于闪存的叙述中,错误的是()

A、信息可读可写,并且读、写速度一样快

B、存储元由MOS管组成,是一种半导体存储器

C、掉电后信息不丢失,是一种非易失性存储器

D、采用随机访问方式,可替代计算机外部存储器

正确答案:A

16.【2015统考真题】下列存储器中,在工作期间需要周期性刷新的是()。

A、SRAM

B、DRAM

C、ROM

D、FLASH

正确答案:B

二、填空题

17.动态半导体存储器的刷新一般有( A )、( B )和 ( C )三种方式,之所以刷新是因为( D )。

正确答案:集中式 分散式 异步式 有电荷泄漏,需定期补充

18.计算机中存储器是用来存放( A )的,随机访问存储器的访问速度与( B )无关。

正确答案:程序和数据 存储位置

19.双译码方式采用( A )个地址译码器,分别产生( B )和( C )信号。

正确答案:两 行选通 列选通

20.一个2M×8位的ROM,其地址线有( A )根,数据线有( B )根

正确答案:21 8

21.构成32M字节的存储器,需要1M×4位的芯片 ( A ) 片。

正确答案:64

22.用M264静态RAM芯片(8K×8)构成48K字节的存储器需要( A )片,芯片上的地址引线有( B )根,CPU要访问该存储器,应该发出( C )位地址。

正确答案:6 13 16

23.要组成一个32K×8位的存储器,当分别选用1K×4位,16K×1位,2K×8位的三种不同规格的存储芯片时,各需 ( A )、( B )和( C )片。

正确答案:64 16 16

24.对存储器的要求是( A ),( B ),( C )为了解决这三方面的矛盾,计算机采用( D )体系结构。

正确答案:容量大 速度快 成本低 多级存储

三、综合题

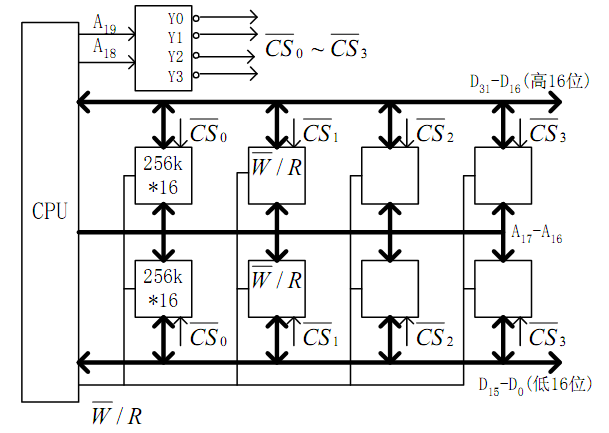

25.要求用 256K×16位 SRAM芯片设计 1024K×32位的存储器。SRAM芯片由两个控制端:当 CS有效时,该片选中。当 W/R=0时执行写操作。

正确答案:

所设计的存储器单元数为 1M,字长为 32,故地址长度为20 位(A19

A0) ,所用芯片存储单元数为 256K,字长为 16 位,故占用的地址长度为 18 位(A17A0)。由此可用位并联方式与地址串联方式相结合的方法组成组成整个存储器,共8 片RAM芯片,并使用一片 2:4译码器。题目解析:

解析:

所设计的存储器单元数为 1M,字长为 32,故地址长度为20 位(A19~A0) ,所用芯片存储单元数为 256K,字长为 16 位,故占用的地址长度为 18 位(A17~A0)。由此可用存储器字长扩展和存储器容量扩展相结合的方法组成整个存储器,共8 片RAM芯片,并使用一片 2:4译码器。其存储器结构如图所示。

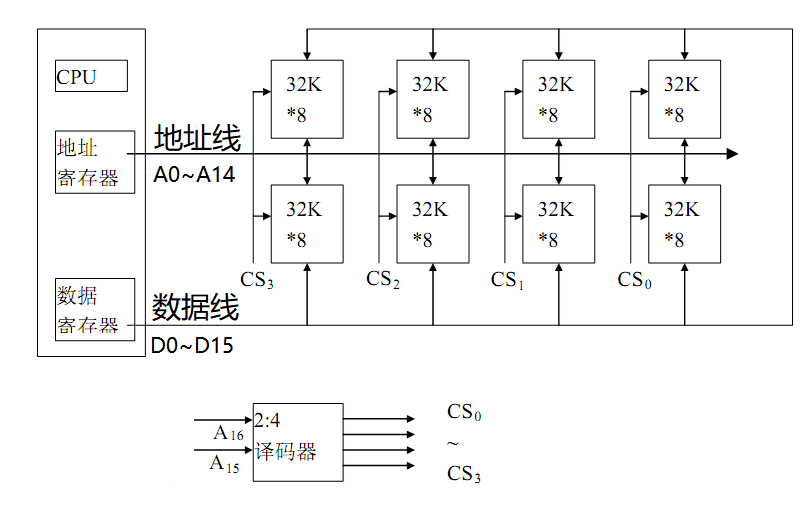

26.用 32K×8位的 EPROM芯片组成 128K×16位的只读存储器,试问:

(1) 数据寄存器是多少位?

(2) 地址寄存器是多少位?

(3) 共需多少块 EPROM芯片?

(4) 画出此存储器组成框图。

正确答案:16、17、8

题目解析:

(1)系统 16位数据,所以数据寄存器16位 (2)系统地址128K=217 ,所以地址寄存器17 位 (3) 共需要 8 片 (4) 组成框图如下:

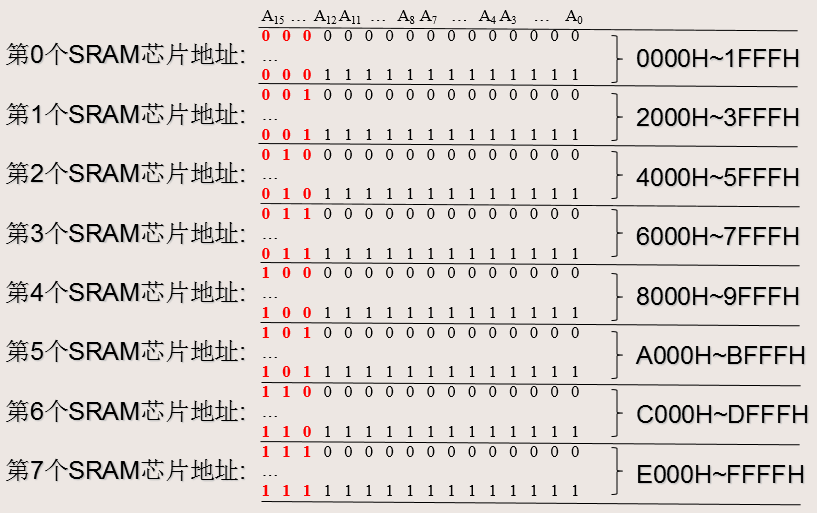

27.设CPU共有16根地址线,8根数据线,并用MREQ(低电平有效)作访存控制信号,R/W作读/写命令信号(高电平为读,低电平为写)。现有若干8K×8位RAM芯片及74138译码器,组成64K存储空间。

** (1)用74138译码器画出CPU与存储芯片的连接图;**

** (2)写出每片RAM的地址范围;

(3)如果运行时发现不论往哪片RAM写入数据,以A000H为起始地址的存储芯片都有与其相同的数据,分析故障原因;

(4)根据(1)的连接图,若出现地址线A13与CPU断线,并搭接到高电平上,将出现什么后果?**

(1)CPU与存储器芯片连接逻辑图:

(2)每片RAM的地址划分:

(3)如果运行时发现不论往哪片RAM写入数据后,以A000H为起始地址的存储芯片都有与其相同的数据,则根本的故障原因为:该存储芯片的片选输入端很可能总是处于低电平。可能的情况有:

** a)该片的CS端与WE端错连或短路;

** b)该片的CS端与CPU的MREQ端错连或短路;

** c)该片的CS端与地线错连或短路;

在此,假设芯片与译码器本身都是好的。**

** d**)译码器故障等。(4)如果地址线A13与CPU断线,并搭接到高电平上,将会出现A13恒为“1”的情况。此时存储器只能寻址A13=1的地址空间,A13=0的另一半地址空间将永远访问不到。若对A13=0的地址空间进行访问,只能错误地访问到A13=1的对应空间中去。

版权归原作者 Yu_chunxuemu 所有, 如有侵权,请联系我们删除。