1 简介

第一次在Xilinx 7series FPGA上实现万兆网UDP设计。具体的实现思路参考米联客的实现方案,但是由于米联客的udp协议栈只提供了网表文件,所以对于他们的内容没有深究,只是用来作为前期链路通断的验证方案。

建议初次上板实现时最好先想办法验证一下硬件,防止硬件有问题导致网络连接不通。

2 硬件部分

2.1 开发板

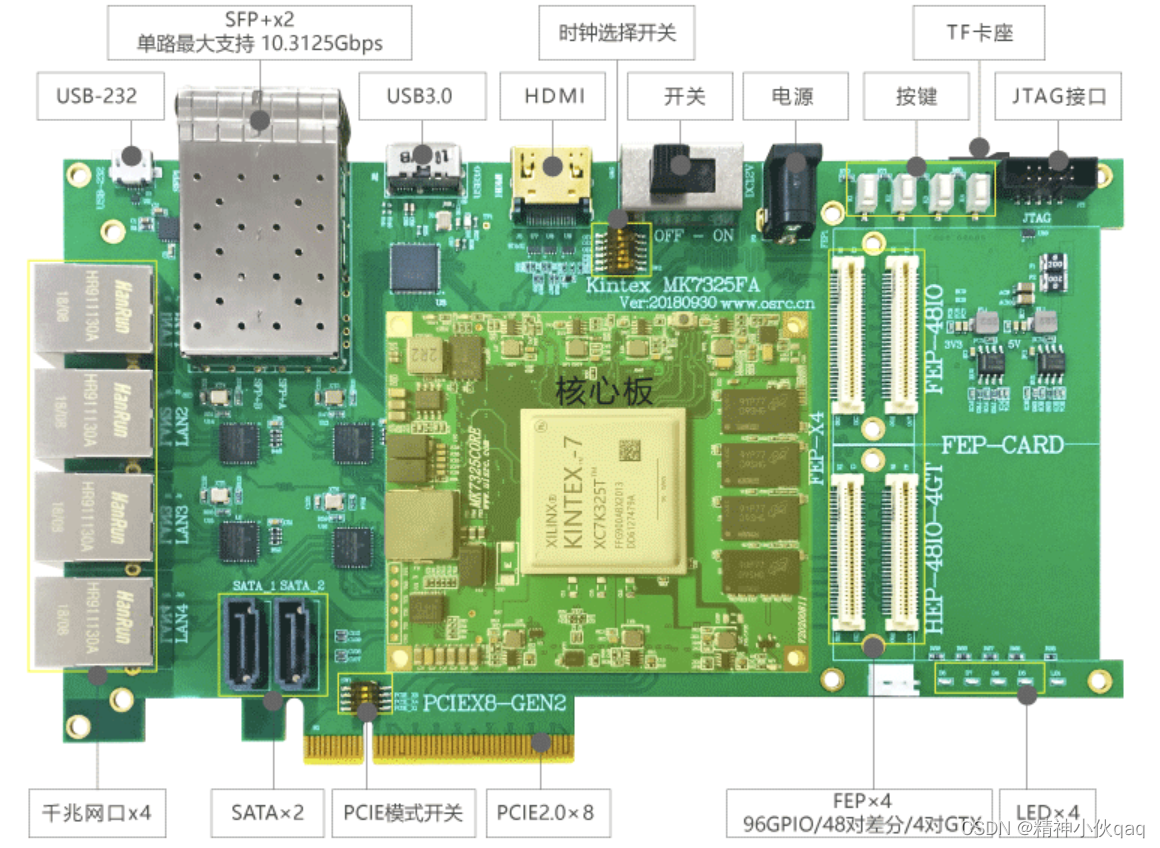

开发板随意,只要带光口就可以。我使用的是米联客 MK7325FA开发板。(最好测试一下GTX的眼图,防止自己制板的不确定性)

2.2 万兆网卡

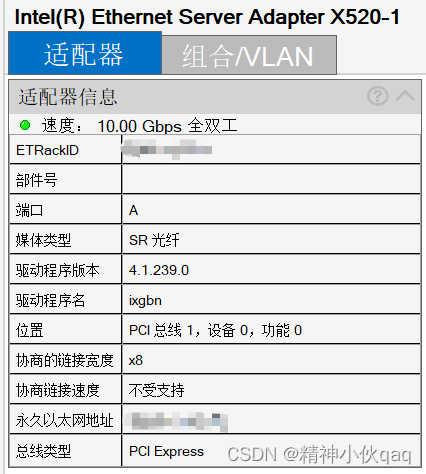

一定要选择可靠的厂家。各家质量参差不齐,我初次使用也不太清楚具体区别。最好选择主控芯片是intel 82599的网卡,支持PCIE3.0 X8。

2.3 光模块

SFP + 单模多模都可以。建议多模,单模的贵 =.=

2.4 光纤

要与光模块匹配,单模的光模块一定要买单模的光纤。

3 实现

3.1 搭建 10g Ethernet Subsystem

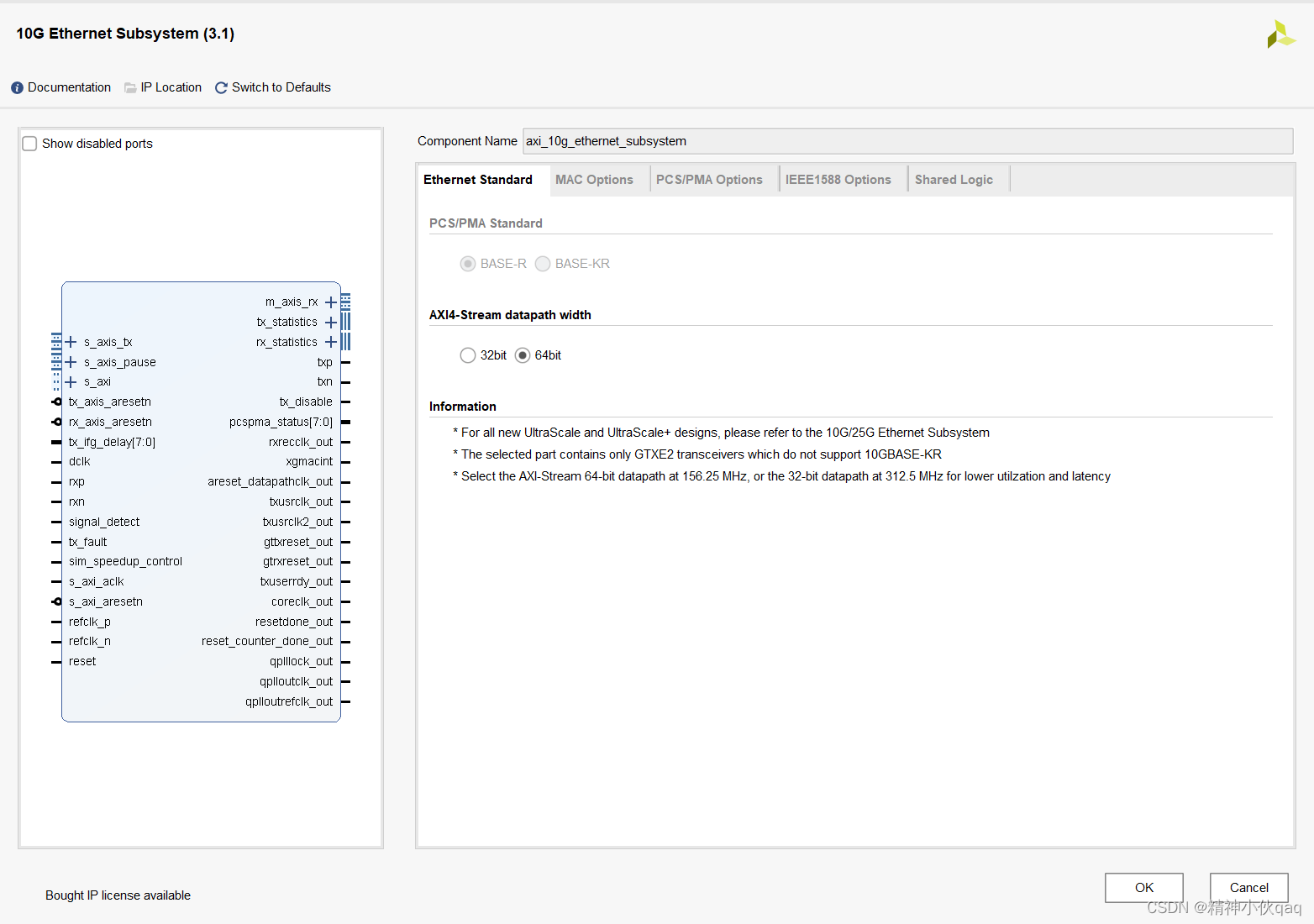

3.1.1 Ethernet Standard

1、PCS/PMA Standard 要选择BASE_R,具体BASE_R和BASE_KR有什么区别我没有深究,但是BASE_KR的lic是要收费的。

2、AXI4-Stream datapath width:选择64bit(8Bytes)。

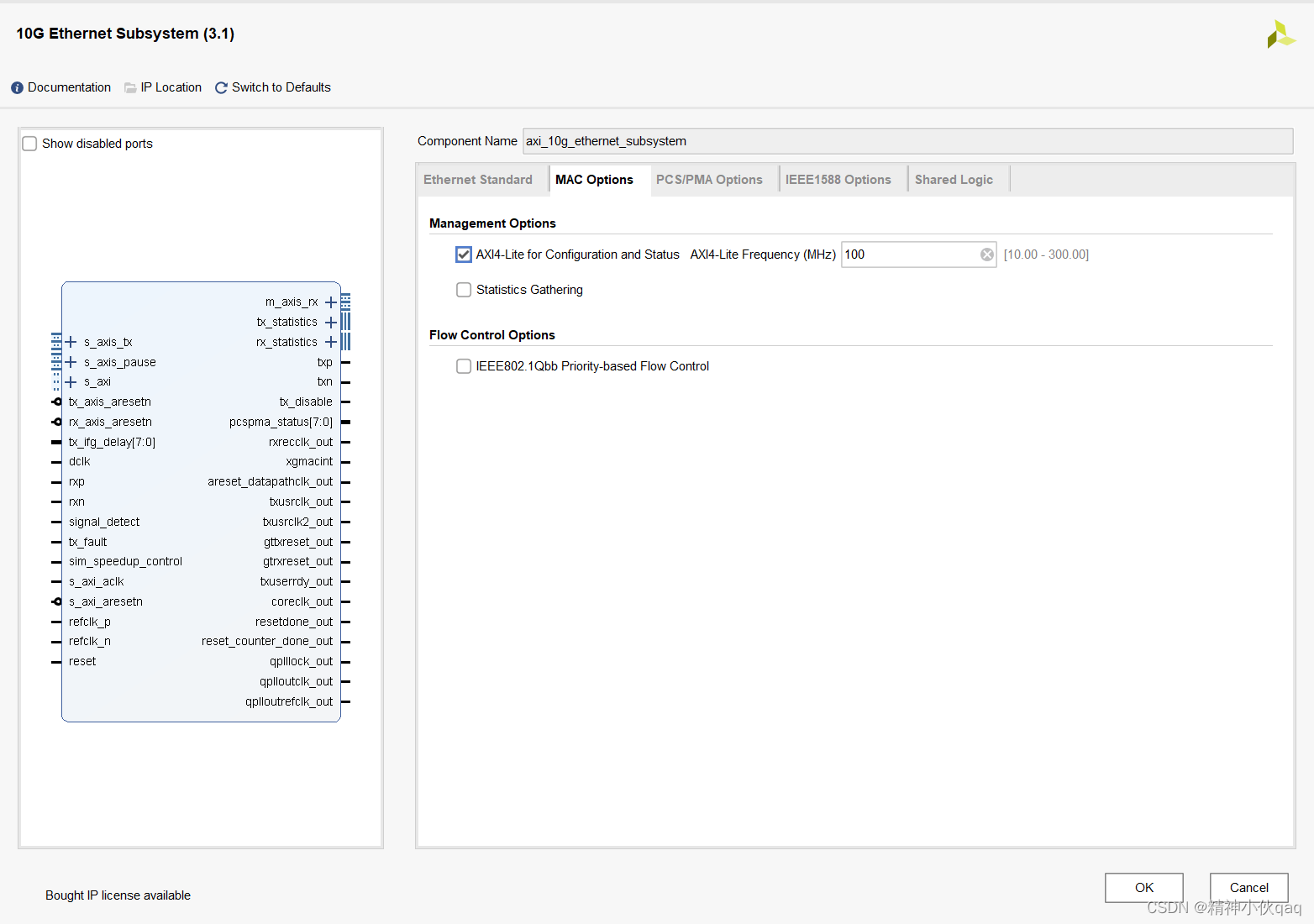

3.1.2 MAC Options

1、勾选AXI4_lite接口,用于配置MAC和访问MAC的状态。时钟建议100MHz。

2、失能流控功能。

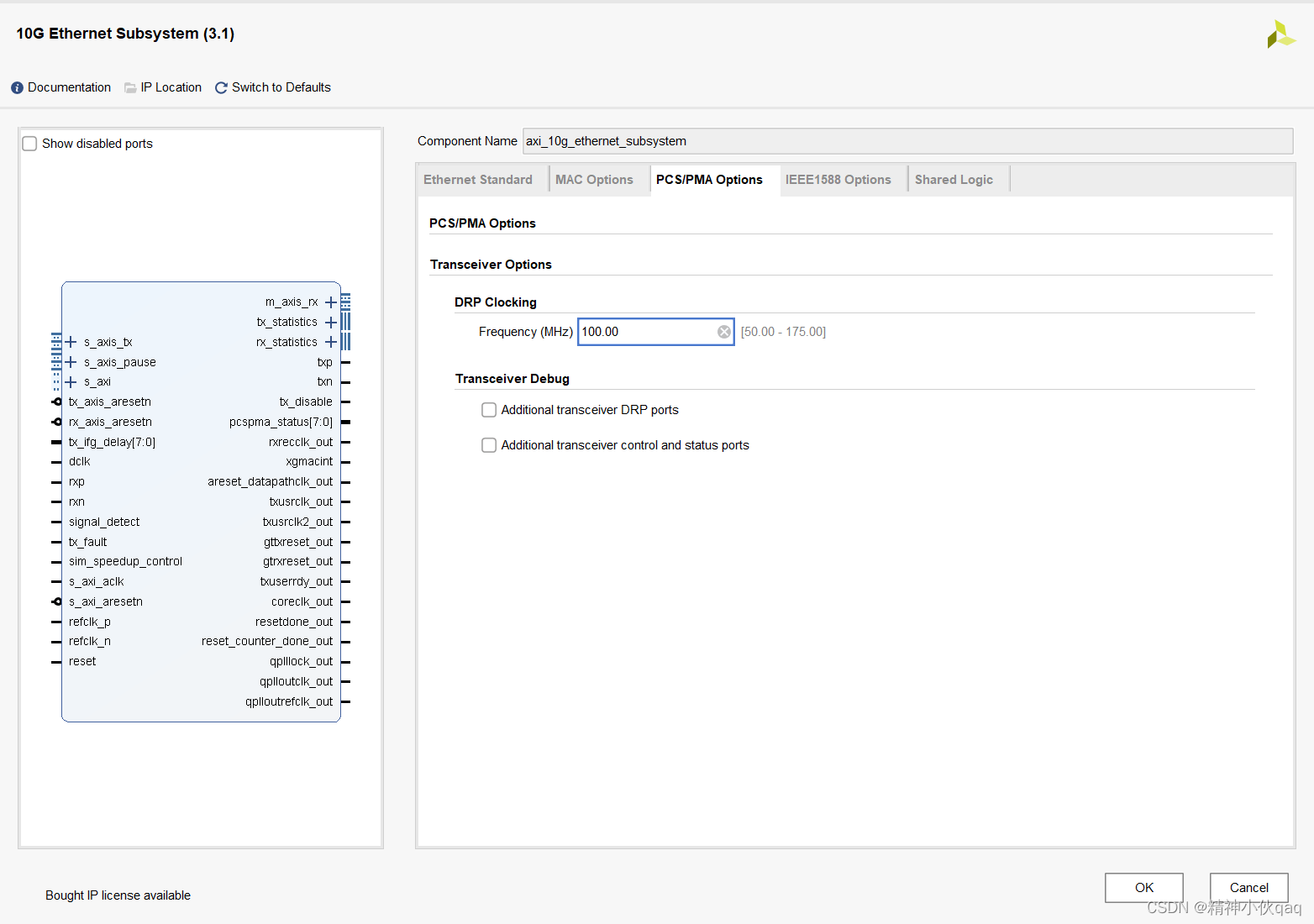

3.1.3 PCS/PMA Options

设置DRP时钟为100MHz。其他的默认即可。

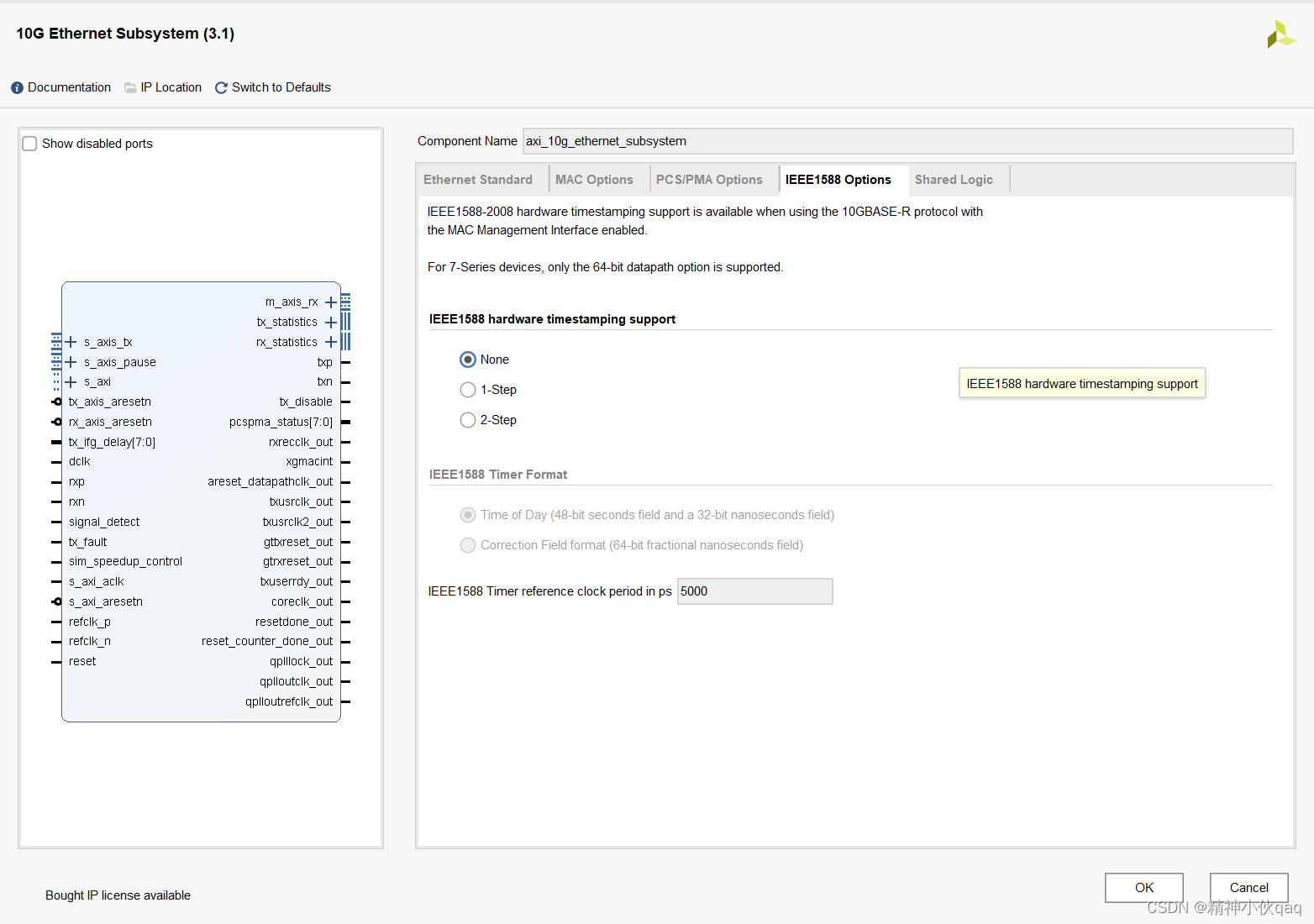

3.1.4 IEEE 1588 Options

不使用1588协议功能。

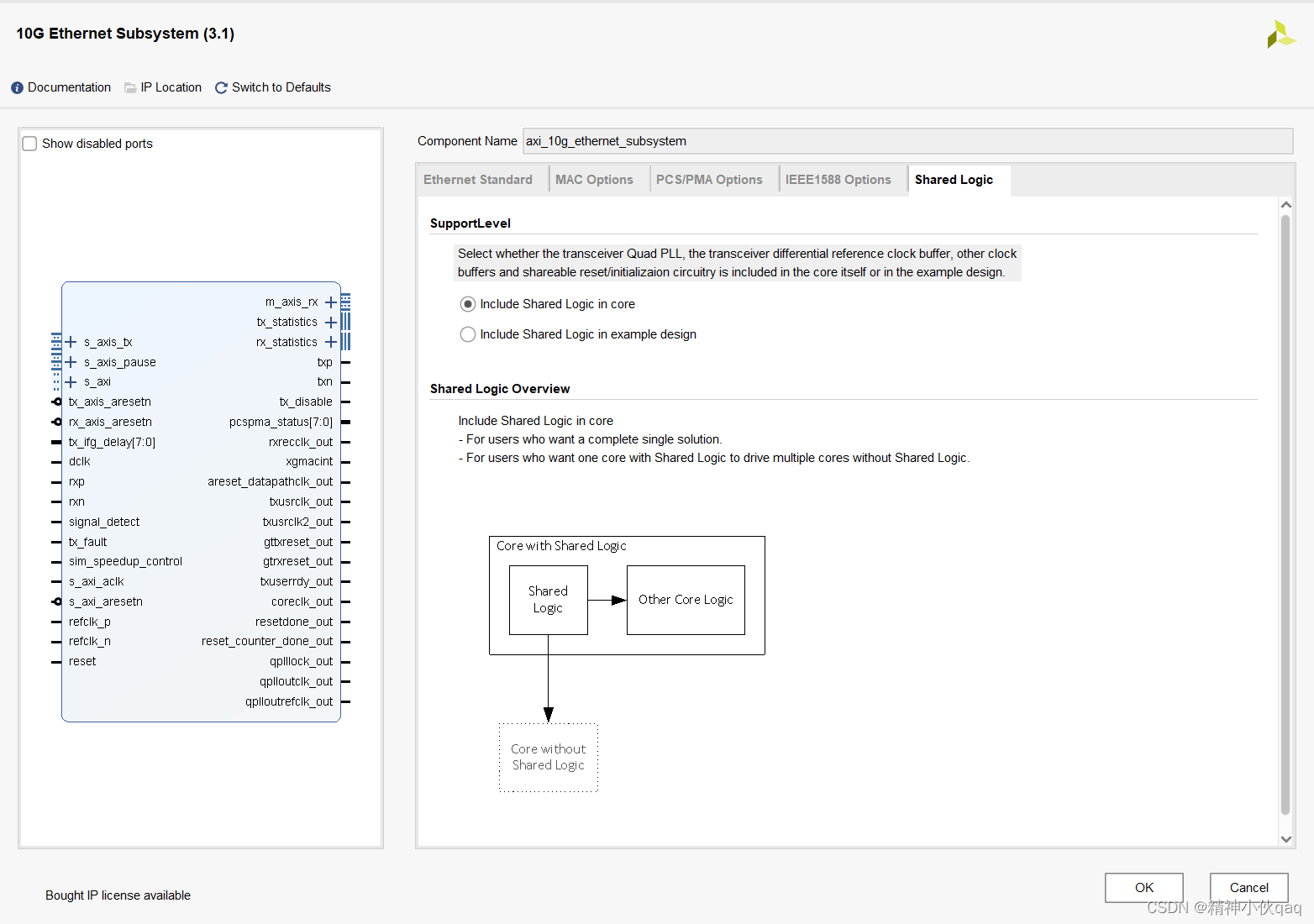

3.1.5 Shared Logic

Include Shared Logic in core。

3.2 10G Ethernet Subsystem架构

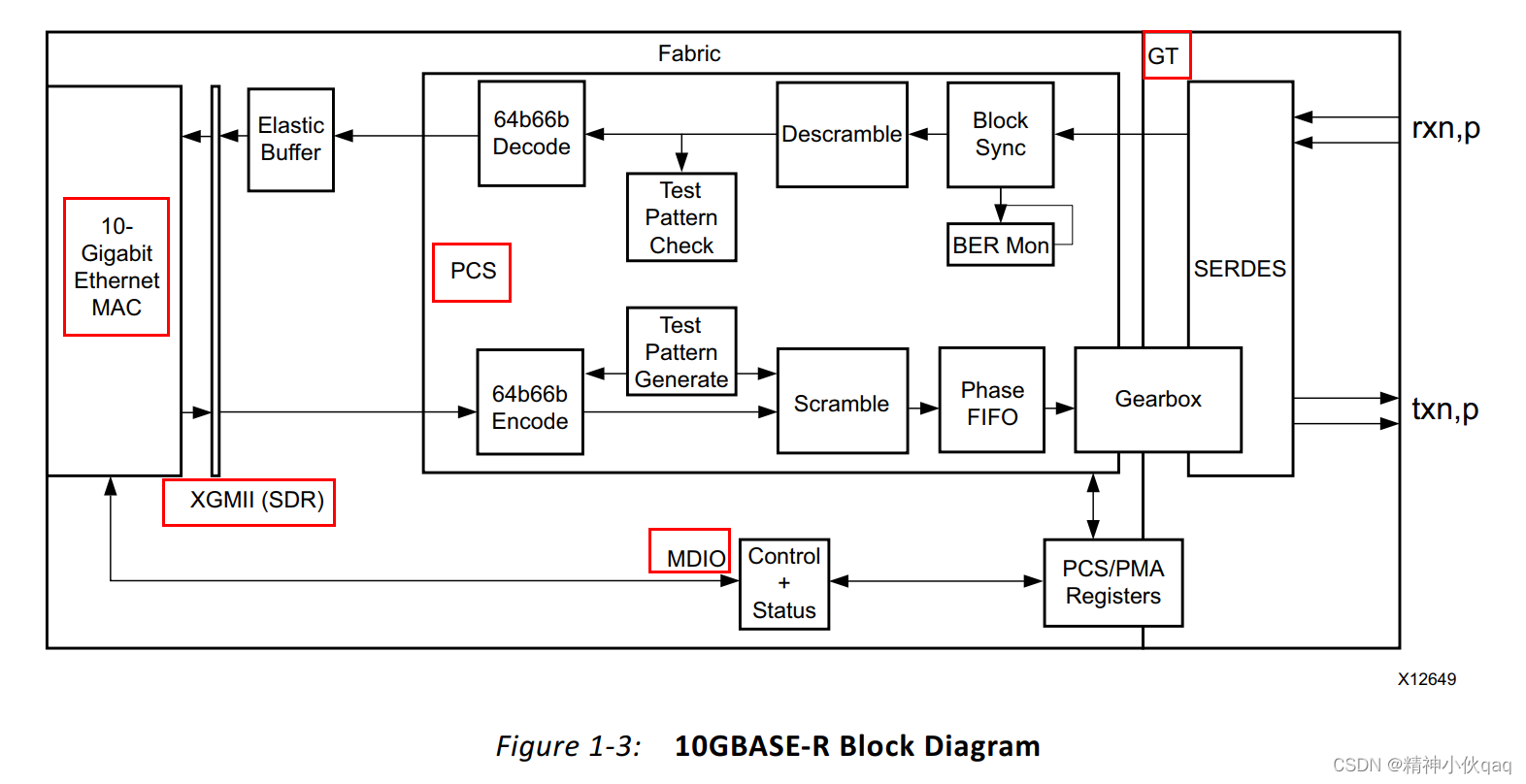

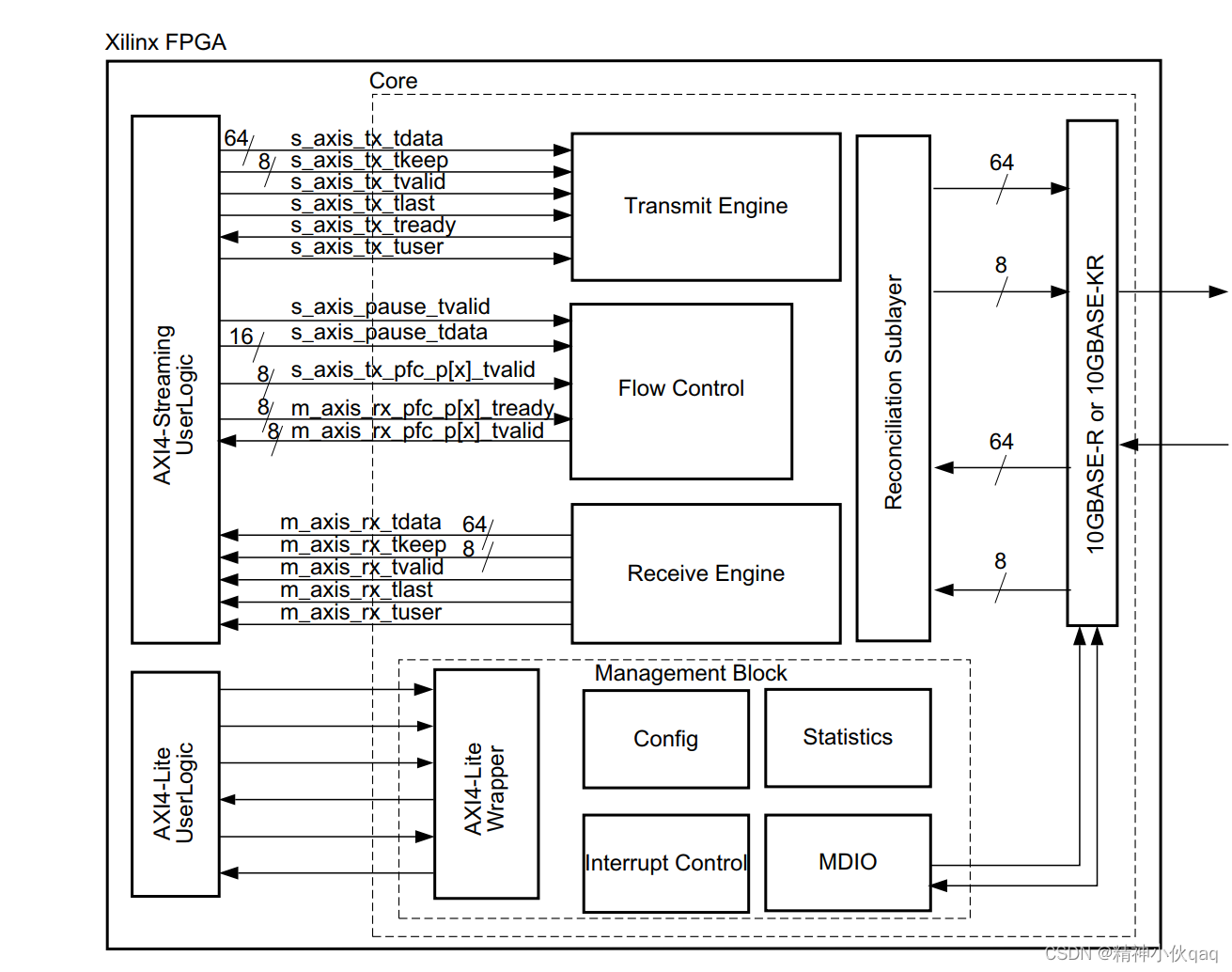

接收数据简单来说就是光信号经光模块转换后的电信号经过xilinx FPGA的GT口进入PCS/PMA。PCS/PMA负责将信号进行数字化,并进行同步和解扰,进经过64b66b译码后送给MAC。PCS/PMA和MAC之间通过XGMII进行数据交换。

MAC 数据分为AXI4_stream和AXI4_lite两部分。AXI4_stream的数据就是以太网帧数据。AXI4_lite是配置MAC的工作方式和状态获取的接口。

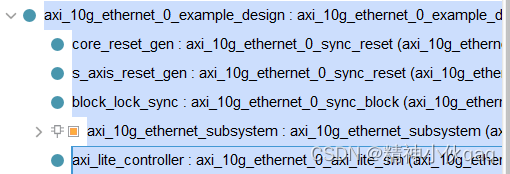

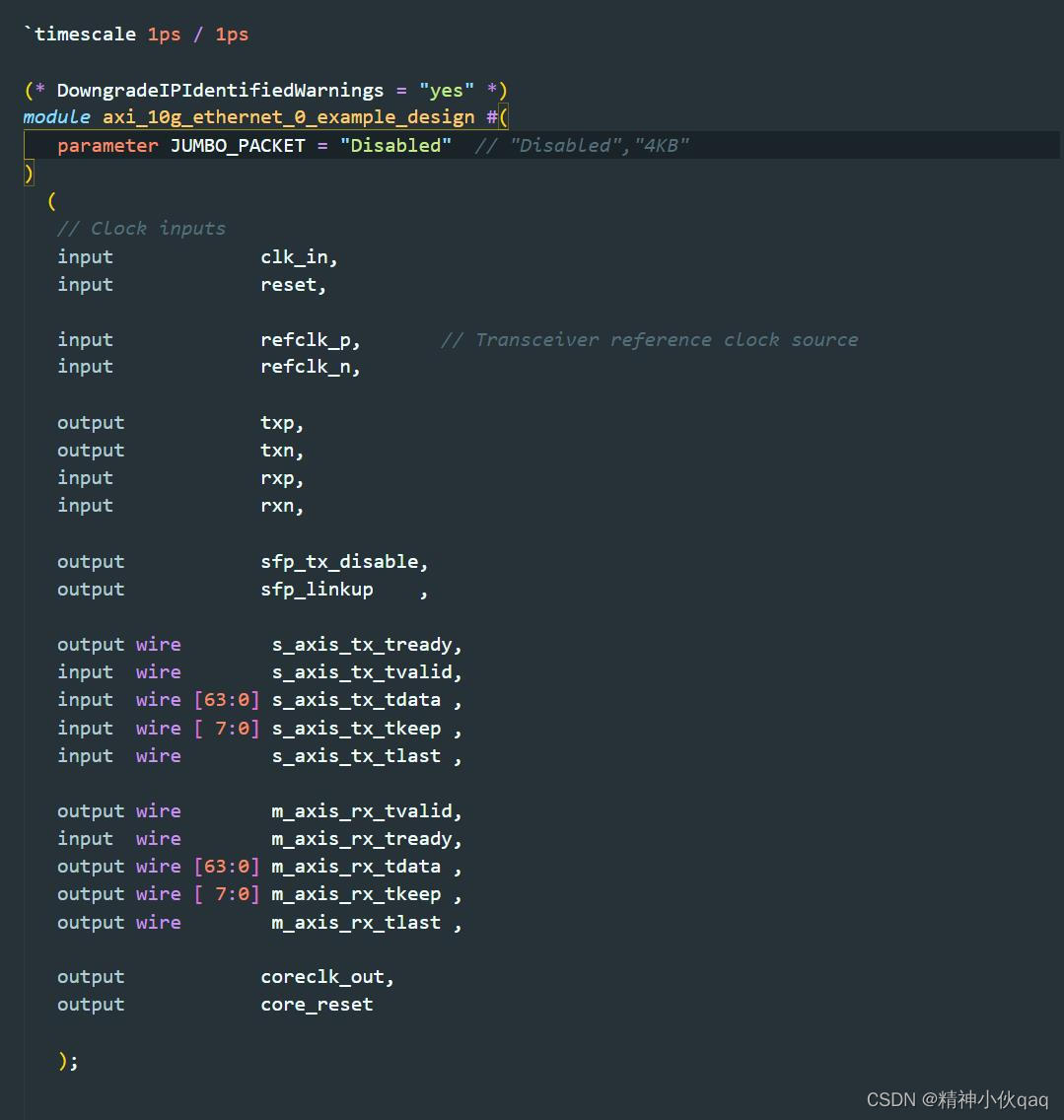

3.3 例化IPCORE

3.3.1 接口

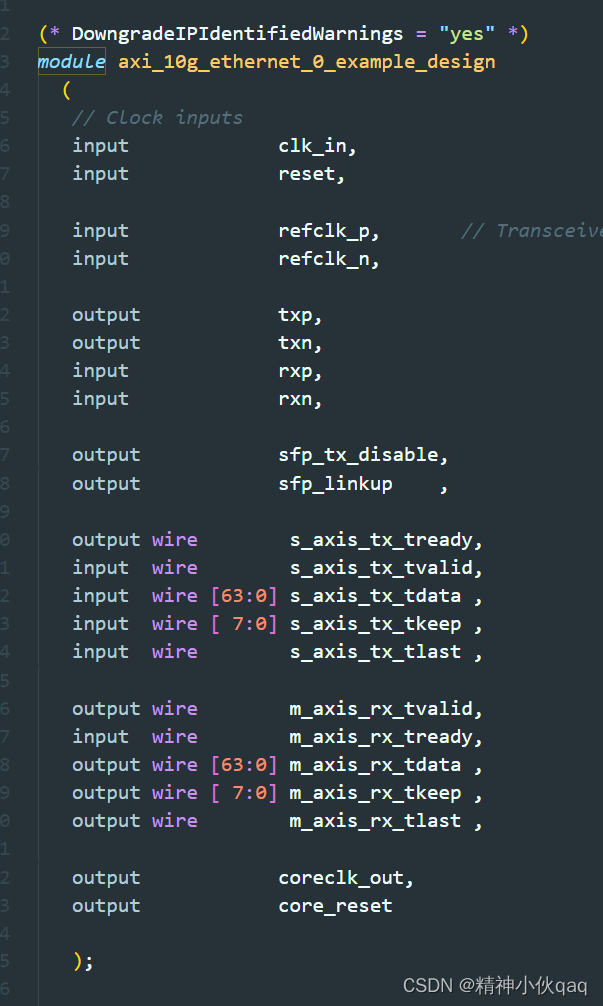

clk_in:输入, 156.25MHz。

reset : 输入,高有效,与clk_in同步。

refclk_p、refclk_n: GT bank参考时钟输入,156.25MHz.

sfp_tx_dis:输出,光模块发送失能,高有效。

sfp_linkup:输出,用于监测光模块与开发板是否连接。

s_axis:MAC核发送数据接口(MAC_tx)。

m_axis:MAC核接收数据接口(MAC_rx)。

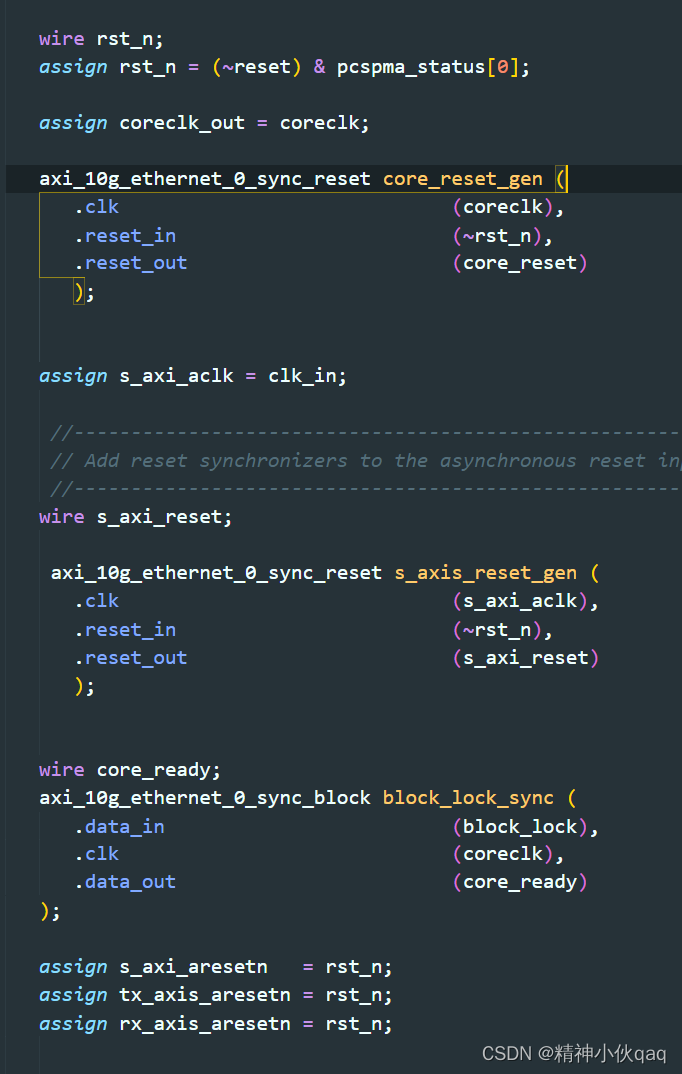

3.3.2 复位

== 一定要等待PCS/PMA复位完成后再复位MAC的相关信号! ==

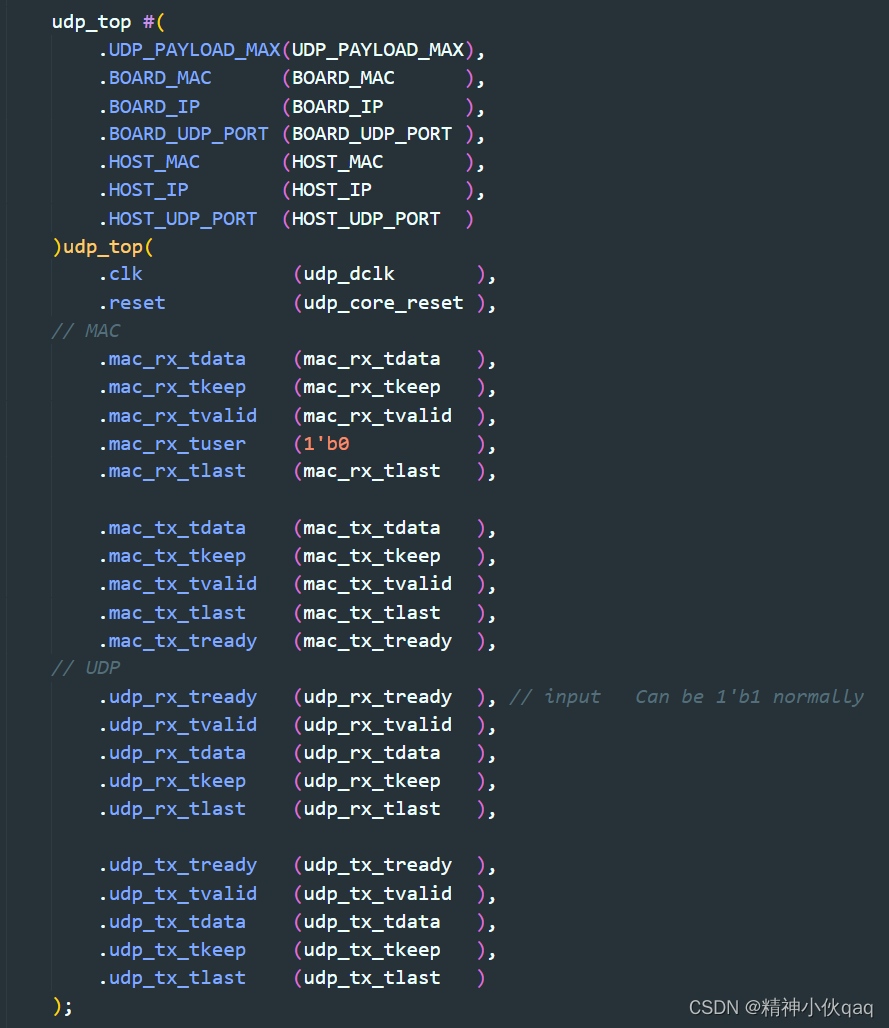

3.4 UDP

这部分就不细说了,有空再细说这部分。我使用的协议栈是在Git_hub上down下来后再自己修改了部分逻辑的。只提供接口,如果想了解内部逻辑的可以圈我。

3.5 工程整体架构

4 测试

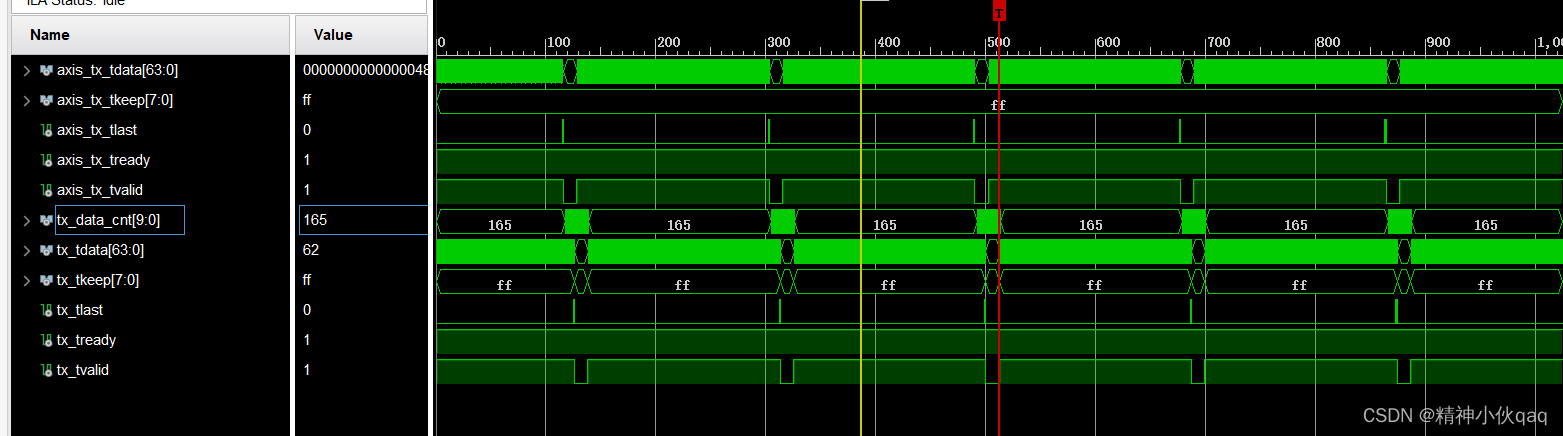

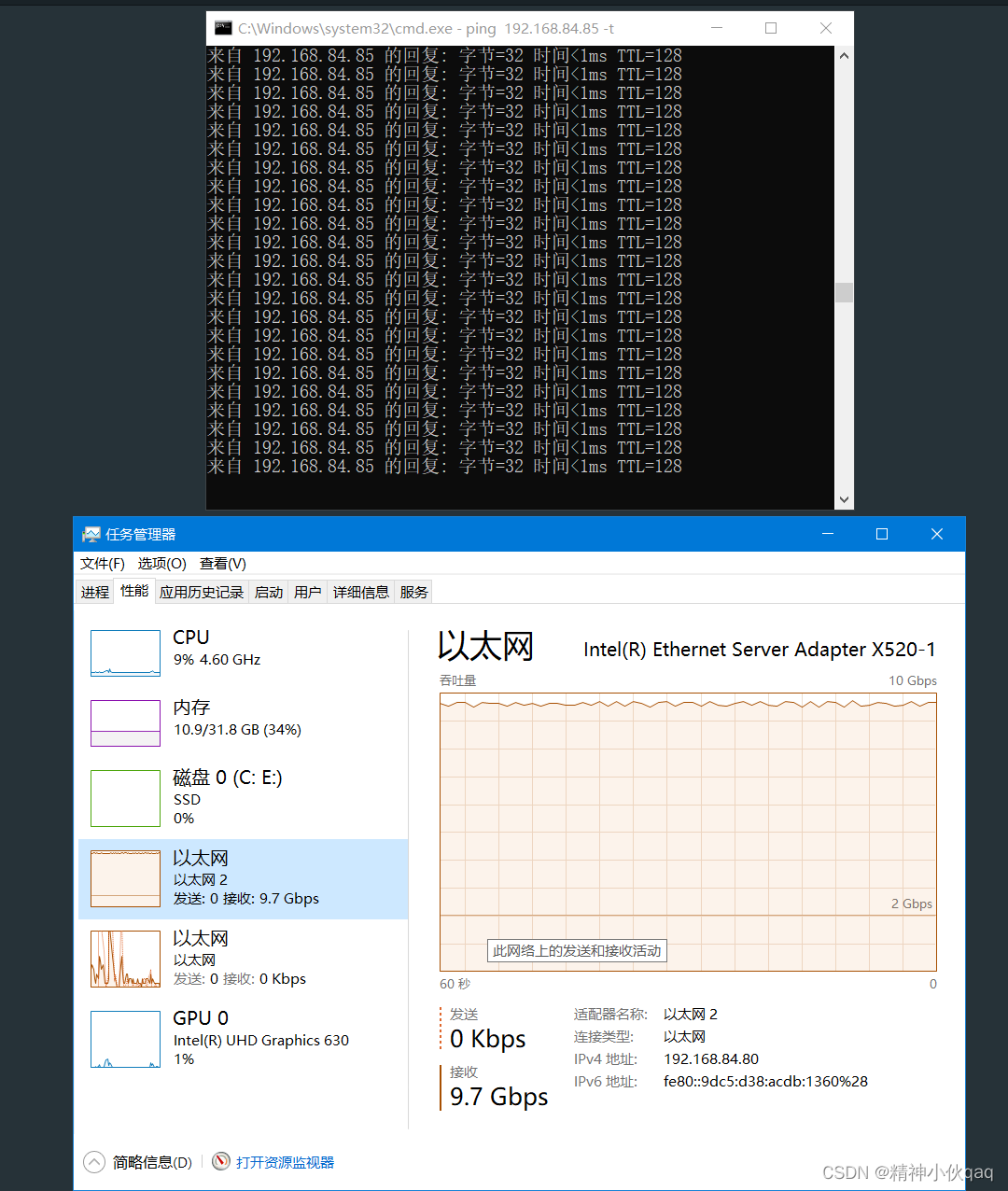

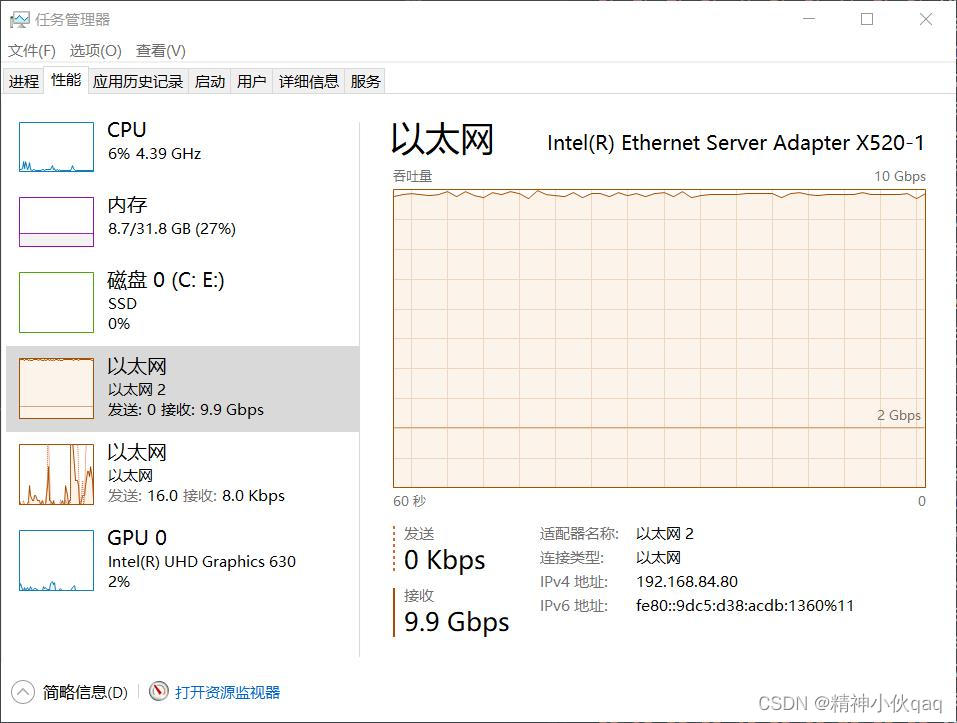

4.1 发送速率测试

实现一边发送数据,一边不间断ping包应答。实测udp发送数据速率可达9.7Gbps。

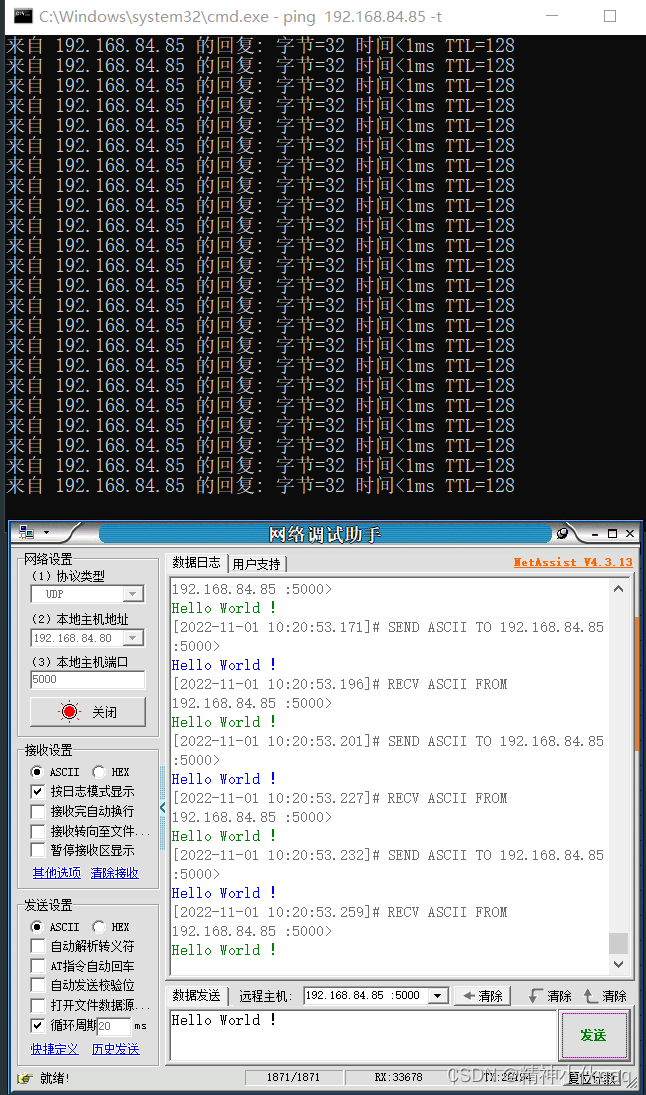

4.2 回环数据测试

实现数据回环且不间断ping包应答。

5 更新

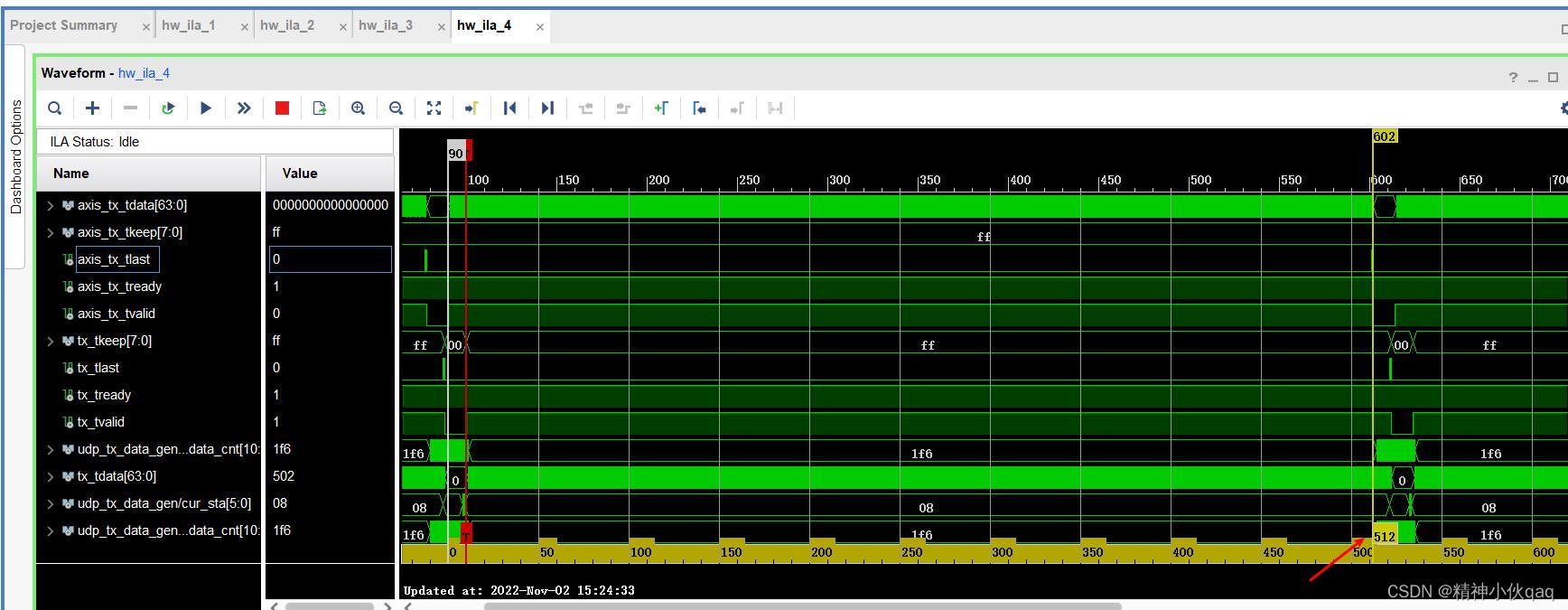

- 20221102 更新 == 修改了UDP协议栈数据缓存架构,现在支持巨帧模式,UDP单包payload最大支持4KB~ == == UDP发送速率稍微提升了一点,现在稳定在9.9Gbps~ ==

- 20221104 更新 == 优化了发送端fifo架构,一定程度上缓解了UDP发送时丢包的问题。~ ==

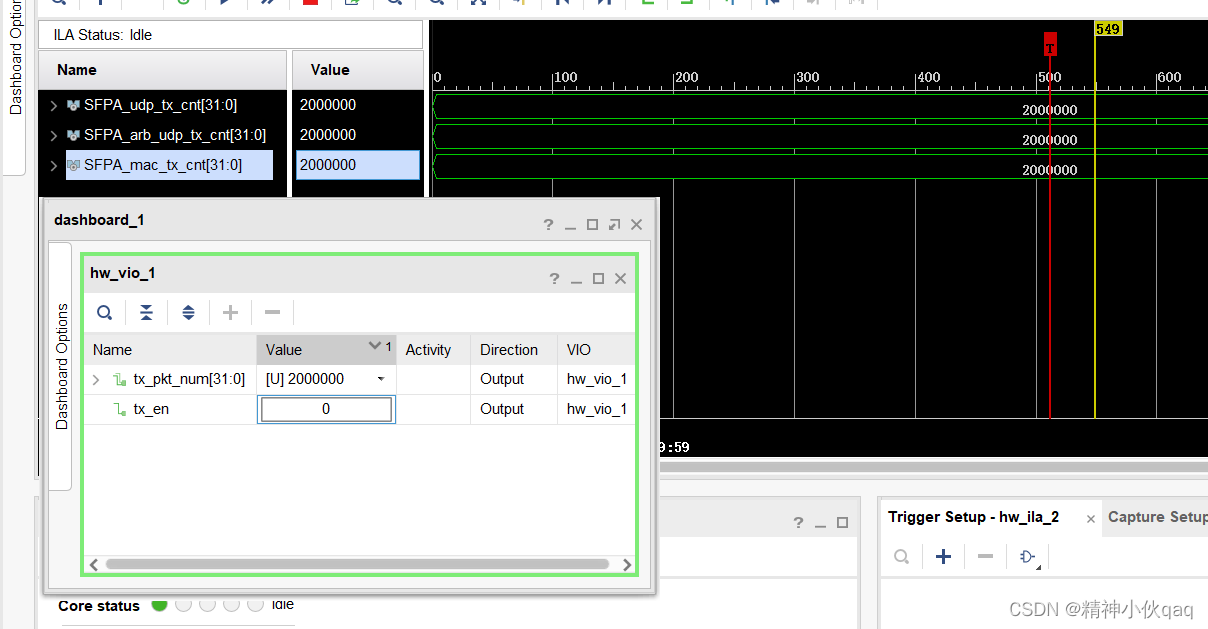

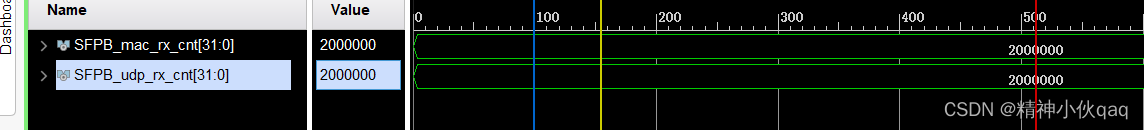

通过光纤实现板上两个SFP+接口互联,将SFPA作为UDP发送端,SFPB作为UDP接收端。

一次触发连续不间断发送200_0000个数据包。

SFPB对应的端口可以正常接收200_0000个数据包,并能正常解出UDP数据包。

测试工程架构如下

版权归原作者 精神小伙qaq 所有, 如有侵权,请联系我们删除。