这篇教程感觉很详细了,我这里分享一下vscode和插件的安装包链接,都是官网下载的,放心食用:

用VSCode编辑verilog代码、iverilog编译、自动例化、自动补全、自动格式化等常用插件

链接:https://pan.baidu.com/s/1zOcb7Ar9YBphjk4cmhs6hg?pwd=mnq4

提取码:mnq4

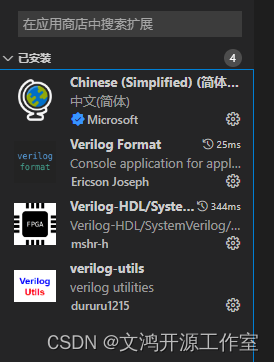

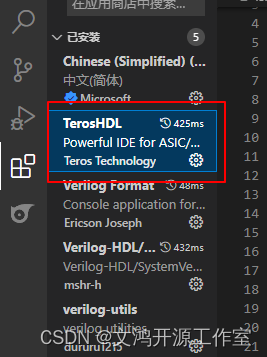

比较有用的插件:

- Chinese 语言包

- Verilog-HDL/SystemVerilog/Bluespec SystemVerilog (识别verilog和sv代码, 查看verilog语法错误)

- verilog-utils (用于自动例化模块)

- Verilog Format

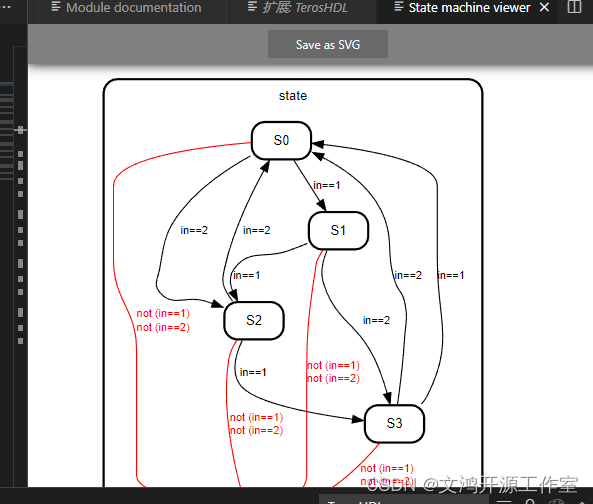

- TerosHDL (这个超级牛,可以生成代码的原理图,状态机转移图,生成说明文档)

1.Verilog-HDL/SystemVerilog/Bluespec SystemVerilog

需要额外安装

- ctags (点击f12,跳转到变量定义的地方)

- 2.iverilog (ctrl+s 保存后,能够识别verilog的语法错误)

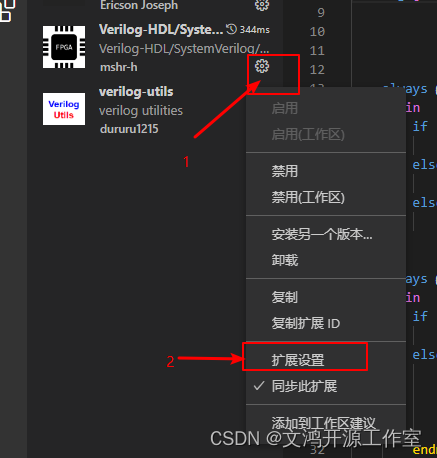

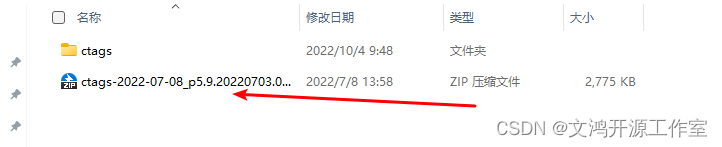

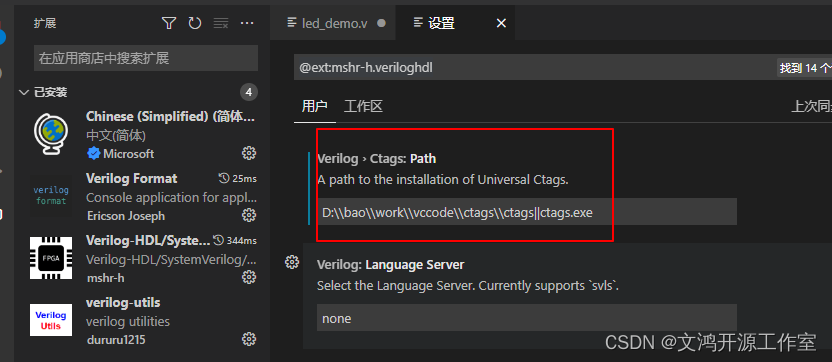

1.ctags 配置。

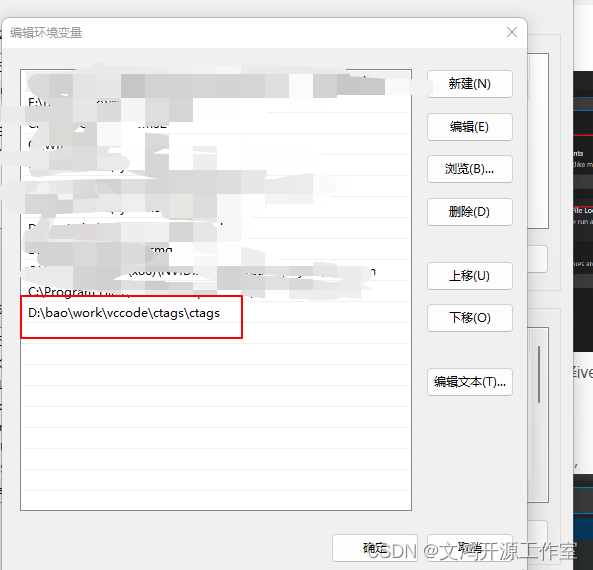

解压压缩包里面的, 在Vs code配置中指向ctags.exe。 格式:D:\bao\work\vccode\ctags\ctags||ctags.exe

在Vs code配置中指向ctags.exe。 格式:D:\bao\work\vccode\ctags\ctags||ctags.exe

打开系统的环境变量,设置系统变量中的PATH,把ctags的目录添加进去

2.iVerilog

iverilog用于编译verilog, 安装了这个,vscode才能够正确的识别verilog语法,查看有没有错误。iverilog的使用教程:全平台轻量开源verilog仿真工具iverilog+GTKWave使用教程

和vcs一样,他需要设定仿真时间,

initial begin

$dumpfile("wave.vcd"); //生成的vcd文件名称

$dumpvars(0, led_demo_tb); //tb模块名称

end

编译:

iverilog -o wave -y ./top.v top_tb.v

-o 生成wave的仿真文件,-y是指,tb中,文件包含了top.v,有这样包含关系的,需要添加-y参数。

运行编译后二进制可执行文件

vvp -n wave -lxt2

生成vcd文件。才能在gtkwave 执行

gtkwave wave.vcd

打开图形化界面,查看波形。

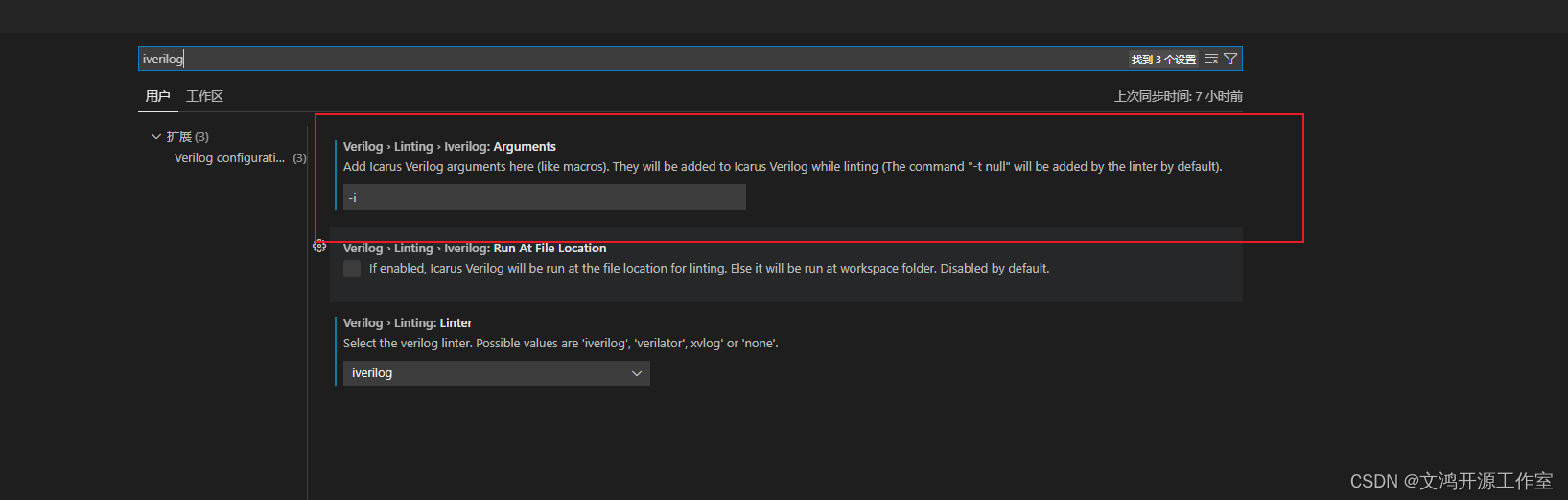

在vscode中,需要添加-i参数。 在linter选择iverilog.

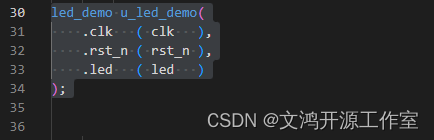

2.verilog_utils

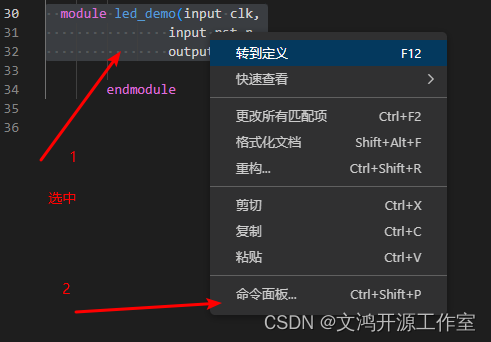

安装好后,选中需要例化的部分,打开命令面板

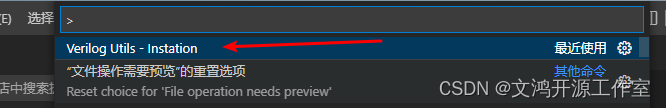

输入utils,找到命令

自动例化后的结果

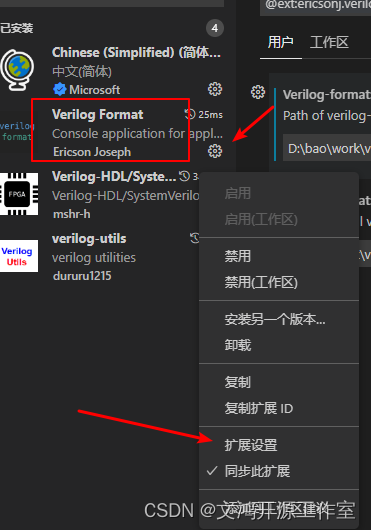

3.Verilog Format

这是一个代码风格化的插件,这需要先安装java, java的安装教程:如何在64位Windows 10下安装java开发环境。

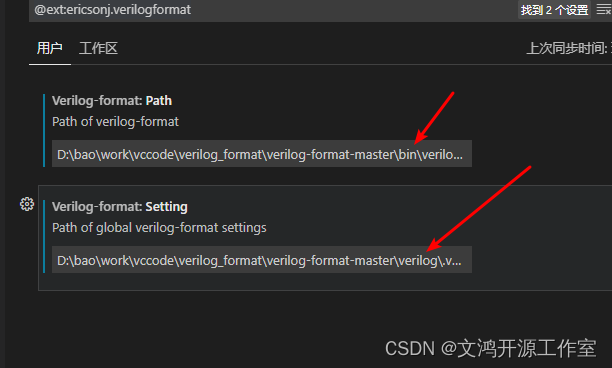

首先在VSCODE插件中,安装Verilog Format, 之后打开Format插件的配置

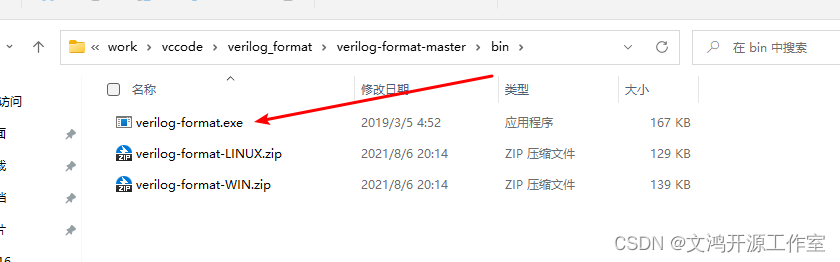

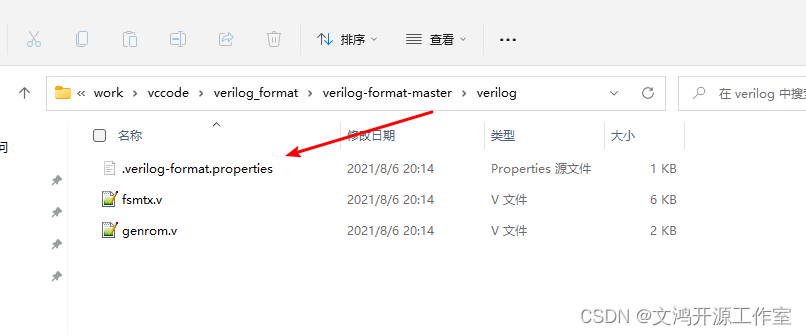

打开我们网盘中的verilog-format-master包。让VScode 内容指向我们的包

第一个配置指向bin的exe

第二个配置指向verilog.verilog-format.properties

4. TerosHDL

参考网址:

- 安装python3 环境,python官网找个最新版安装一下就行。

- 在VSCODE插件中,安装TerosHDL。

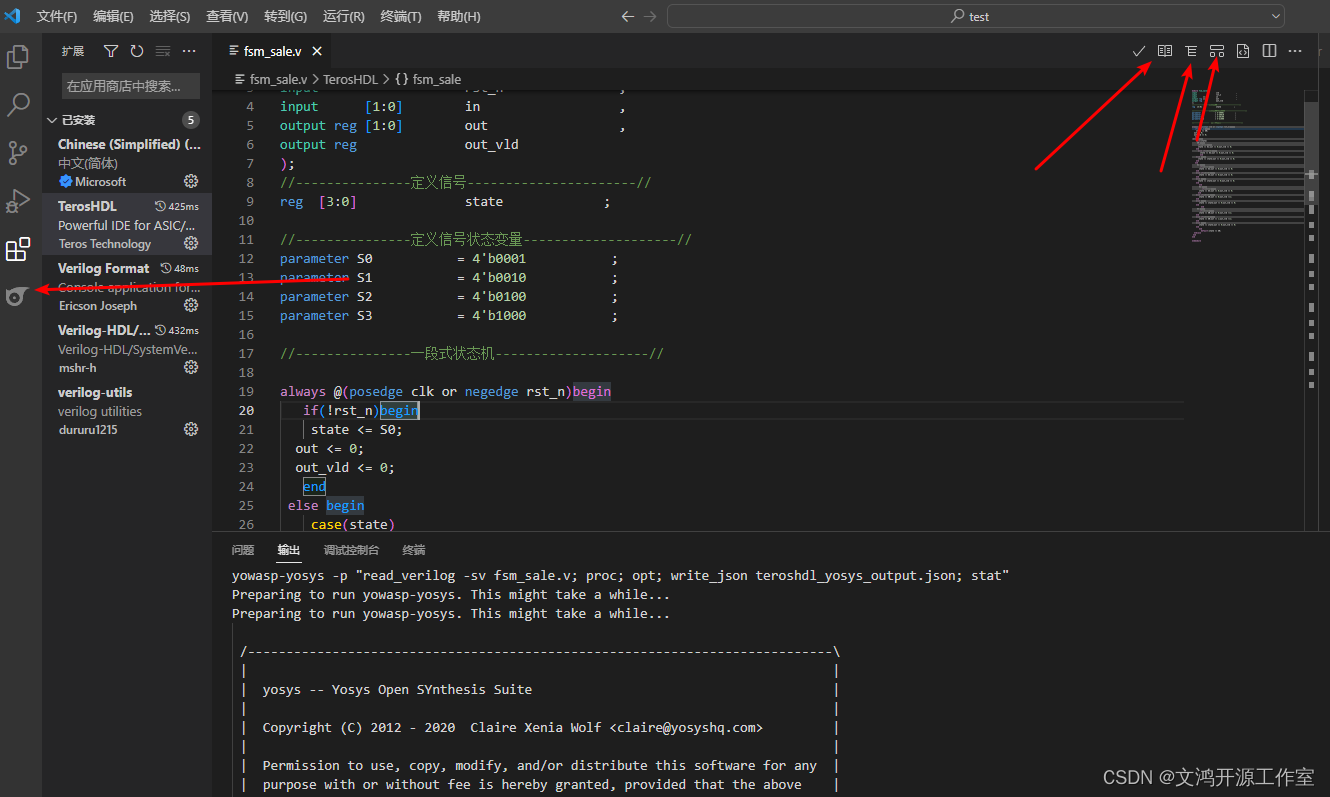

配置完成后,在界面的右上角有几个选项。

配置完成后,在界面的右上角有几个选项。 可以用来查看状态机转移图,原理图,说明文档这些。

可以用来查看状态机转移图,原理图,说明文档这些。 配置完环境变量需要重启VSCODE。

配置完环境变量需要重启VSCODE。

版权归原作者 ChipChatter 所有, 如有侵权,请联系我们删除。