简介

Aurora 是一个用于在点对点串行链路间移动数据的可扩展轻量级链路层协议。这为物理层提供透明接口,让专有协议或业界标准协议上层能方便地使用高速收发器。虽然使用的逻辑资源非常少,但 Aurora 能提供低延迟高带宽和高度可配置的特性集。

特性:

高带宽,仅受限于收发器的数据速率

支持大量键合线路,实现较高的总带宽

支持全双工和单工通道

无限帧尺寸/灵活组帧

小型逻辑封装,采用标准的 AXI-ST 接口。

内置流程控制和热插拔支持

Aurora 广泛用于需要背板、电路板间和芯片间连接的应用。细分市场包括有线通信、存储、服务器、测试测量、工业、消费和医疗等。此外,Aurora 也可用作嵌入式处理器应用中的调试端口

速率

Aurora 64B/66B核心吞吐量取决于收发器数量、收发器类型和所选收发器的目标线速率

对于GTH收发器,从单车道设计到16车道设计,吞吐量分别为0.48 Gb/s到254.06 Gb/s。GTY收发器的吞吐量范围为0.455 Gb/s ~ 400gb /s,支持的线路速率范围为0.5 Gb/s ~ 25.7813 Gb/s。当线路速率大于16.375 Gb/s时,考虑到设计中的车道分条差异,GTY的最大吞吐量可能不准确

64B/66B编码相对8B/10B编码提供了理论上的性能提升,因为它的传输开销非常低(3%),而8B/10B编码的传输开销为25%

66B/64B编码

64B/66B编码将64bit数据或控制信息编码成66bit块传输,66bit块的前两位表示同步头,主要由于接收端的数据对齐和接收数据位流的同步。同步头有“01”和“10”两种,“01“表示后面的64bit都是数据,“10”表示后面的64bit是数据信息。

数据信息0和1不一定是平衡的,因此需要进行加扰。

64b/66b编码没有办法限制Run Length(即数据流中的连续的0或者连续的1长度)到一个比较小的值,只能通过选择合适的多项式来取得相对最优的DC Balance和相对较低的较大值得Run Length的概率。显然,采用64b/66b编码,对串行收发器的CDR提出了非常高的要求。

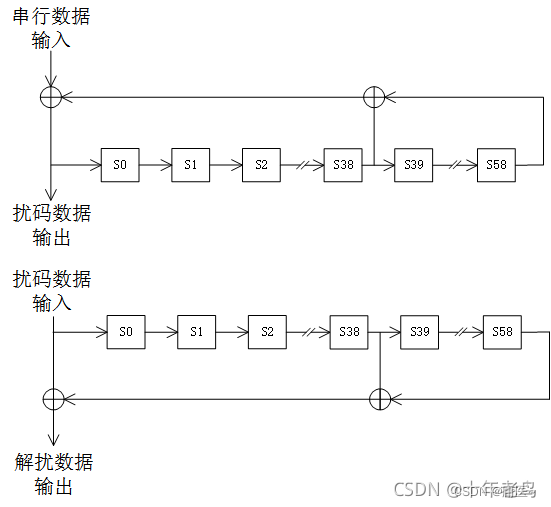

扰码

扰码的数学原理使用了多项式,多项式的选择通常是基于扰码的特性,包括生成数据的随机度,以及打乱连0和连1的能力。一个简单的扰码器包含一组排列好的触发器,用于移位数据流。大部分的触发器只需要简单地输出下一个比特流即可,但是在复杂的扰码电路中,触发器需要与数据流中的历史比特进行逻辑运算(与和或运算)

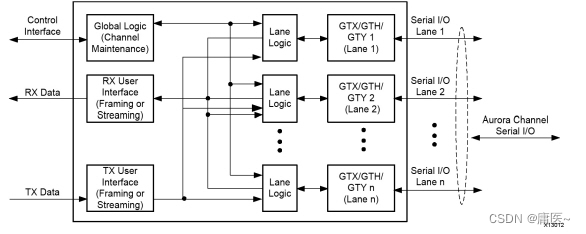

64B/66B核心的主要功能模块

•通道逻辑:每个GT收发器由通道逻辑模块的实例驱动,该模块初始化每个收发器,处理控制字符的编码和解码,并执行错误检测。

•全局逻辑:核心中的全局逻辑模块为通道初始化执行通道绑定。在操作期间,通道跟踪由Aurora 64B/66B协议定义的Not Ready空闲字符,并监视所有通道逻辑模块的错误。

•RX用户界面:axis - stream接收(RX)用户界面将数据从通道移动到应用程序,并执行流量控制功能。

•TX用户界面:axis - stream传输(TX)用户界面将数据从应用程序移动到通道,还执行流控制TX功能。标准时钟补偿模块嵌在核心内部。该模块控制时钟补偿(CC)字符的周期性传输。

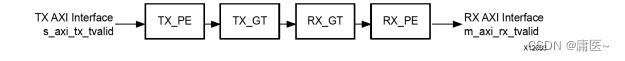

通道延时

对于默认的单通道配置,通过Aurora 64B/66B核心的延迟是由通过协议引擎(PE)以及通过GTX和GTH收发器的管道延迟引起的。PE管道延迟随着AXI4-Stream接口宽度的增加而增加。收发器延迟由收发器特性决定。

为了说明延迟,Aurora 64B/66B模块在GTX、GTH和GTY收发器中的逻辑和FPGA中实现的协议引擎(PE)逻辑之间进行了分区。

该图说明了数据路径的延迟。

版权归原作者 庸医~ 所有, 如有侵权,请联系我们删除。