一、设计要求

1.利用 NEXYS4 DDR 开发板设计一款数字时钟,能够正确显示时、分、秒;

2.数字时钟为24小时进制;

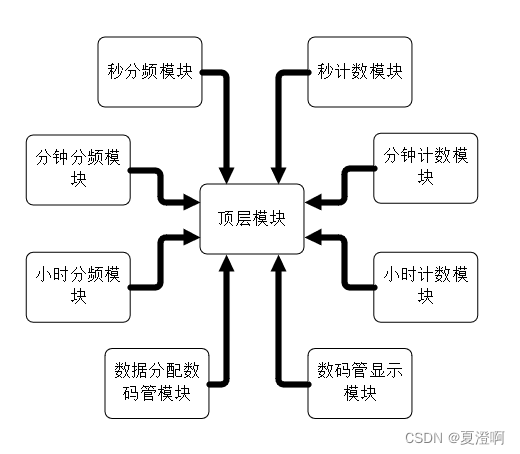

二、模块总和

三、模块设计

1.顶层模块

module digital_clock_top(

input clk,

input rst_n,

output [7:0]sel,

output [7:0]seg

);

wire clk_1s;

wire clk_1f;

wire clk_1h;

wire [5:0]cnt_s;

wire [5:0]cnt_f;

wire [4:0]cnt_h;

wire [3:0]bit_s;

wire [3:0]tenbit_s;

wire [3:0]bit_f;

wire [3:0]tenbit_f;

wire [3:0]bit_h;

wire [3:0]tenbit_h;

digital_clock_div_s a(

.clk(clk),

.rst_n(rst_n),

.clk_1s(clk_1s)

);

digital_clock_count_s b(

.clk(clk_1s),

.rst_n(rst_n),

.cnt_s(cnt_s)

);

digital_clock_div_f c(

.clk(clk),

.rst_n(rst_n),

.clk_1f(clk_1f)

);

digital_clock_count_f d(

.clk(clk_1f),

.rst_n(rst_n),

.cnt_f(cnt_f)

);

digital_clock_div_h e(

.clk(clk),

.rst_n(rst_n),

.clk_1h(clk_1h)

);

digital_clock_count_h f(

.clk(clk_1h),

.rst_n(rst_n),

.cnt_h(cnt_h)

);

digital_clock_time g(

.clk(clk),

.rst_n(rst_n),

.cnt_s(cnt_s),

.cnt_f(cnt_f),

.cnt_h(cnt_h),

.bit_s(bit_s),

.tenbit_s(tenbit_s),

.bit_f(bit_f),

.tenbit_f(tenbit_f),

.bit_h(bit_h),

.tenbit_h(tenbit_h)

);

digital_clock_digital h(

.clk(clk),

.rst_n(rst_n),

.bit_s(bit_s),

.tenbit_s(tenbit_s),

.bit_f(bit_f),

.tenbit_f(tenbit_f),

.bit_h(bit_h),

.tenbit_h(tenbit_h),

.sel(sel),

.seg(seg)

);

endmodule

2.秒分频模块

module digital_clock_div_s(

input clk,

input rst_n,

output reg clk_1s

);

//计数器计数1s的数值

reg [25:0]cnt1;

always @(posedge clk or negedge rst_n)

if(!rst_n)

cnt1 <= 0;

else if(cnt1 == 26'd49999999)

cnt1 <= 0;

else

cnt1 <= cnt1 + 1;

//分频为1s

always @(posedge clk or negedge rst_n)

if(!rst_n)

clk_1s <= 0;

else if(cnt1 == 26'd49999999)

clk_1s <= ~clk_1s;

else

clk_1s <= clk_1s;

endmodule

3.秒计数模块

module digital_clock_count_s(

input clk,

input rst_n,

output reg [5:0]cnt_s //计数60秒

);

always @(negedge clk or negedge rst_n)

if(!rst_n)

cnt_s <= 0;

else if(cnt_s == 6'd59)

cnt_s <= 0;

else

cnt_s <= cnt_s + 1;

endmodule

4.分钟分频模块

module digital_clock_div_f(

input clk,

input rst_n,

output reg clk_1f

);

//计数器计数1分钟的数值

reg [31:0]cnt2;//计数值 ((60000000000/10=6000000000)/2-1)=2,999,999,999

always @(posedge clk or negedge rst_n)

if(!rst_n)

cnt2 <= 0;

else if(cnt2 == 32'd2999999999)

cnt2 <= 0;

else

cnt2 <= cnt2 + 1;

//分频为1分钟

always @(posedge clk or negedge rst_n)

if(!rst_n)

clk_1f <= 0;

else if(cnt2 == 32'd2999999999)

clk_1f <= ~clk_1f;

else

clk_1f <= clk_1f;

endmodule

5.分钟计数模块

module digital_clock_count_f(

input clk,

input rst_n,

output reg [5:0]cnt_f //计数60分

);

always @(negedge clk or negedge rst_n)

if(!rst_n)

cnt_f <= 0;

else if(cnt_f == 6'd59)

cnt_f <= 0;

else

cnt_f <= cnt_f + 1;

endmodule

6.小时分频模块

module digital_clock_div_h(

input clk,

input rst_n,

output reg clk_1h

);

//计数器计数1小时的数值

reg [37:0]cnt3;//计数值 ((3600000000000/10=360000000000)/2-1)=179,999,999,999

always @(posedge clk or negedge rst_n)

if(!rst_n)

cnt3 <= 0;

else if(cnt3 == 38'd179999999999)

cnt3 <= 0;

else

cnt3 <= cnt3 + 1;

//分频为1分钟

always @(posedge clk or negedge rst_n)

if(!rst_n)

clk_1h <= 0;

else if(cnt3 == 38'd179999999999)

clk_1h <= ~clk_1h;

else

clk_1h <= clk_1h;

endmodule

7.小时计数模块

module digital_clock_count_h(

input clk,

input rst_n,

output reg [4:0]cnt_h //计数24小时

);

always @(negedge clk or negedge rst_n)

if(!rst_n)

cnt_h <= 0;

else if(cnt_h == 5'd23)

cnt_h <= 0;

else

cnt_h <= cnt_h + 1;

endmodule

8.数据分配数码管模块

module digital_clock_time(

input clk,

input rst_n,

input [5:0]cnt_s,

input [5:0]cnt_f,

input [4:0]cnt_h,

output reg [3:0]bit_s,//个位秒

output reg [3:0]tenbit_s,//十位秒

output reg [3:0]bit_f,//个位分

output reg [3:0]tenbit_f,//十位分

output reg [3:0]bit_h,//个位时

output reg [3:0]tenbit_h //十位时

);

always @(posedge clk or negedge rst_n )

if(!rst_n)

begin

bit_s <= 0;

tenbit_s <= 0;

end

else if (cnt_s < 6'd10)

begin

bit_s <= (cnt_s%10);

tenbit_s <= 0;

end

else if (cnt_s < 6'd20)

begin

bit_s <= (cnt_s - 10);

tenbit_s <= 1;

end

else if (cnt_s < 6'd30)

begin

bit_s <= (cnt_s - 20);

tenbit_s <= 2;

end

else if (cnt_s < 6'd40)

begin

bit_s <= (cnt_s - 30);

tenbit_s <= 3;

end

else if (cnt_s < 6'd50)

begin

bit_s <= (cnt_s - 40);

tenbit_s <= 4;

end

else if (cnt_s <= 6'd59)

begin

bit_s <= (cnt_s - 50);

tenbit_s <= 5;

end

always @(posedge clk or negedge rst_n )

if(!rst_n)

begin

bit_f <= 0;

tenbit_f <= 0;

end

else if (cnt_f < 6'd10)

begin

bit_f <= (cnt_f%10);

tenbit_f <= 0;

end

else if (cnt_f < 6'd20)

begin

bit_f <= (cnt_f - 10);

tenbit_f <= 1;

end

else if (cnt_f < 6'd30)

begin

bit_f <= (cnt_f - 20);

tenbit_f <= 2;

end

else if (cnt_f < 6'd40)

begin

bit_f <= (cnt_f - 30);

tenbit_f <= 3;

end

else if (cnt_f < 6'd50)

begin

bit_f <= (cnt_f - 40);

tenbit_f <= 4;

end

else if (cnt_f <= 6'd59)

begin

bit_f <= (cnt_f - 50);

tenbit_f <= 5;

end

always @(posedge clk or negedge rst_n )

if(!rst_n)

begin

bit_h <= 0;

tenbit_h <= 0;

end

else if (cnt_h < 5'd10)

begin

bit_h <= (cnt_h%10);

tenbit_h <= 0;

end

else if (cnt_h < 5'd20)

begin

bit_h <= (cnt_h - 10);

tenbit_h <= 1;

end

else if (cnt_h < 5'd23)

begin

bit_h <= (cnt_h - 20);

tenbit_h <= 2;

end

endmodule

9.数码管显示模块

module digital_clock_digital(

input clk,

input rst_n,

input [3:0]bit_s,//个位秒

input [3:0]tenbit_s,//十位秒

input [3:0]bit_f,//个位分

input [3:0]tenbit_f,//十位分

input [3:0]bit_h,//个位时

input [3:0]tenbit_h, //十位时

output reg [7:0]sel,//片选信号

output reg [7:0]seg //段选信号

);

//1ms计数器

reg [16:0]cnt4;

always @(posedge clk or negedge rst_n)

if(!rst_n)

cnt4 <= 0;

else if(cnt4 == 99999)//1000000/10=100000

cnt4 <= 0;

else

cnt4 <= cnt4 + 1;

//1ms使能时钟控制信号

reg clk_1ms;

always @(posedge clk or negedge rst_n)

if(!rst_n)

clk_1ms <= 0;

else if(cnt4 == 99999)

clk_1ms <= 1;

else

clk_1ms <= 0;

//位选计数器

reg [2:0]num_cnt;

always @(posedge clk or negedge rst_n)

if(!rst_n)

num_cnt <= 0;

else if(clk_1ms)

num_cnt <= num_cnt + 1;

//板上位选信号 共阳极 低电平有效

always @(posedge clk)

case(num_cnt)

0:sel <=8'b1111_1110;//个位

1:sel <=8'b1111_1101;//十位

2:sel <=8'b1111_1011;

3:sel <=8'b1111_0111;

4:sel <=8'b1110_1111;

5:sel <=8'b1101_1111;

6:sel <=8'b1111_1111;

7:sel <=8'b1111_1111;

endcase

//数据分配

wire [31:0]data;

assign data[3:0] = bit_s;

assign data[7:4] = tenbit_s;

assign data[11:8] = bit_f;

assign data[15:12] = tenbit_f;

assign data[19:16] = bit_h;

assign data[23:20] = tenbit_h;

/*assign data[27:24] = 0;

assign data[31:28] = 0; */

reg [3:0]disp_tmp;

always @(posedge clk)

case(num_cnt)

0:disp_tmp <= data[3:0];

1:disp_tmp <= data[7:4];

2:disp_tmp <= data[11:8];

3:disp_tmp <= data[15:12];

4:disp_tmp <= data[19:16];

5:disp_tmp <= data[23:20];

6:disp_tmp <= data[27:24];

7:disp_tmp <= data[31:28];

endcase

//板上段选信号 共阳极 低电平有效

always @(posedge clk)

case(disp_tmp)

4'd0:seg <= 8'b1100_0000;

4'd1:seg <= 8'b1111_1001;

4'd2:seg <= 8'b1010_0100;

4'd3:seg <= 8'b1011_0000;

4'd4:seg <= 8'b1001_1001;

4'd5:seg <= 8'b1001_0010;

4'd6:seg <= 8'b1000_0010;

4'd7:seg <= 8'b1111_1000;

4'd8:seg <= 8'b1000_0000;

4'd9:seg <= 8'b1001_0000;

endcase

endmodule

10.管脚约束代码

set_property IOSTANDARD LVCMOS33 [get_ports {seg[7]}]

set_property IOSTANDARD LVCMOS33 [get_ports {seg[6]}]

set_property IOSTANDARD LVCMOS33 [get_ports {seg[5]}]

set_property IOSTANDARD LVCMOS33 [get_ports {seg[4]}]

set_property IOSTANDARD LVCMOS33 [get_ports {seg[3]}]

set_property IOSTANDARD LVCMOS33 [get_ports {seg[2]}]

set_property IOSTANDARD LVCMOS33 [get_ports {seg[1]}]

set_property IOSTANDARD LVCMOS33 [get_ports {seg[0]}]

set_property IOSTANDARD LVCMOS33 [get_ports {sel[7]}]

set_property IOSTANDARD LVCMOS33 [get_ports {sel[6]}]

set_property IOSTANDARD LVCMOS33 [get_ports {sel[5]}]

set_property IOSTANDARD LVCMOS33 [get_ports {sel[4]}]

set_property IOSTANDARD LVCMOS33 [get_ports {sel[3]}]

set_property IOSTANDARD LVCMOS33 [get_ports {sel[2]}]

set_property IOSTANDARD LVCMOS33 [get_ports {sel[1]}]

set_property IOSTANDARD LVCMOS33 [get_ports {sel[0]}]

set_property IOSTANDARD LVCMOS33 [get_ports clk]

set_property IOSTANDARD LVCMOS33 [get_ports rst_n]

set_property PACKAGE_PIN E3 [get_ports clk]

set_property PACKAGE_PIN C12 [get_ports rst_n]

set_property PACKAGE_PIN U13 [get_ports {sel[7]}]

set_property PACKAGE_PIN K2 [get_ports {sel[6]}]

set_property PACKAGE_PIN T14 [get_ports {sel[5]}]

set_property PACKAGE_PIN P14 [get_ports {sel[4]}]

set_property PACKAGE_PIN J14 [get_ports {sel[3]}]

set_property PACKAGE_PIN T9 [get_ports {sel[2]}]

set_property PACKAGE_PIN J18 [get_ports {sel[1]}]

set_property PACKAGE_PIN J17 [get_ports {sel[0]}]

set_property PACKAGE_PIN R10 [get_ports {seg[1]}]

set_property PACKAGE_PIN K16 [get_ports {seg[2]}]

set_property PACKAGE_PIN K13 [get_ports {seg[3]}]

set_property PACKAGE_PIN P15 [get_ports {seg[4]}]

set_property PACKAGE_PIN T11 [get_ports {seg[5]}]

set_property PACKAGE_PIN L18 [get_ports {seg[6]}]

set_property PACKAGE_PIN H15 [get_ports {seg[7]}]

set_property PACKAGE_PIN T10 [get_ports {seg[0]}]

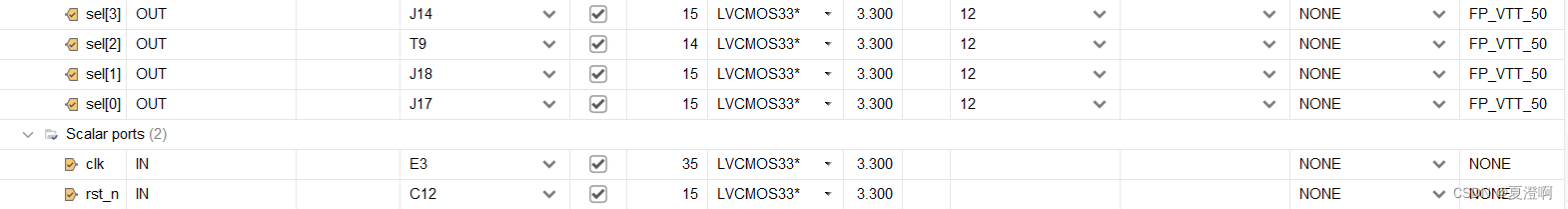

四、引脚分配

本文转载自: https://blog.csdn.net/m0_57283507/article/details/131184040

版权归原作者 夏澄啊 所有, 如有侵权,请联系我们删除。

版权归原作者 夏澄啊 所有, 如有侵权,请联系我们删除。