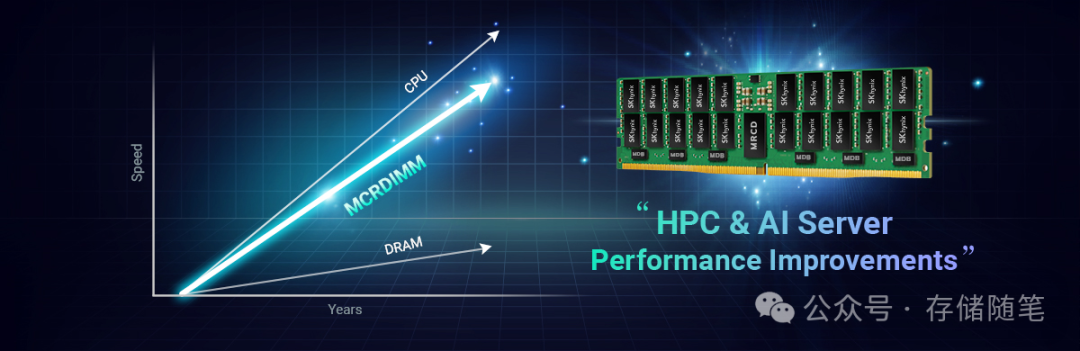

随着云计算、大数据、人工智能(AI)和高性能计算(HPC)等领域对内存带宽的迫切需求,存储技术的创新显得尤为重要。在这个背景下,MCR DIMM(Multiplexer Combined Ranks DIMM)应运而生,成为解决内存带宽瓶颈的关键技术之一。

基础阅读:

- 论文解读|数据中心内存RAS技术全景剖析

- 数据中心:AI范式下的内存挑战与机遇

- 一文读懂DDR内存基础知识|值得收藏

- 如何利用CXL技术突破内存墙?

- 3D DRAM:突破内存瓶颈的新希望

随着处理器核心数的不断增加,为处理器提供足够的内存带宽一直是行业面临的挑战,特别是在数据中心领域,AMD的EPYC和Intel的Xeon处理器核心数已达到数十甚至上百核。MRDIMM技术的提出,为解决这一问题提供了新的策略,尤其是在双路或四路服务器配置中,能够有效利用有限主板空间提升整体内存带宽。

MCR DIMM(或者称为MRDIMM)的开发源于对更高性能、更高效能比的内存解决方案的迫切需求。传统的DRAM模块受限于每次只能向CPU传输有限数据量的问题,通常为64字节,这在处理大数据量和高并发任务时成为性能瓶颈。随着AI、大数据和HPC应用的兴起,数据处理速度和吞吐量的要求日益剧增,迫使业界寻找新的解决方案以打破这一局限。

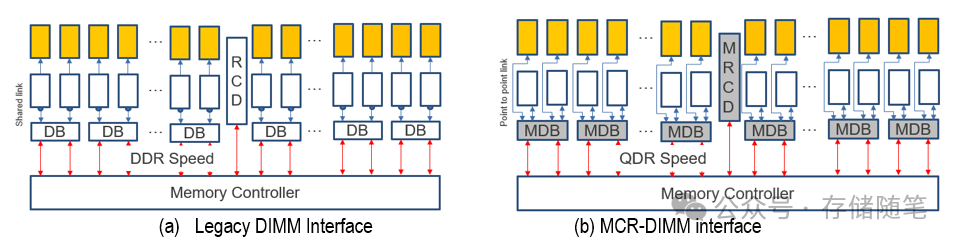

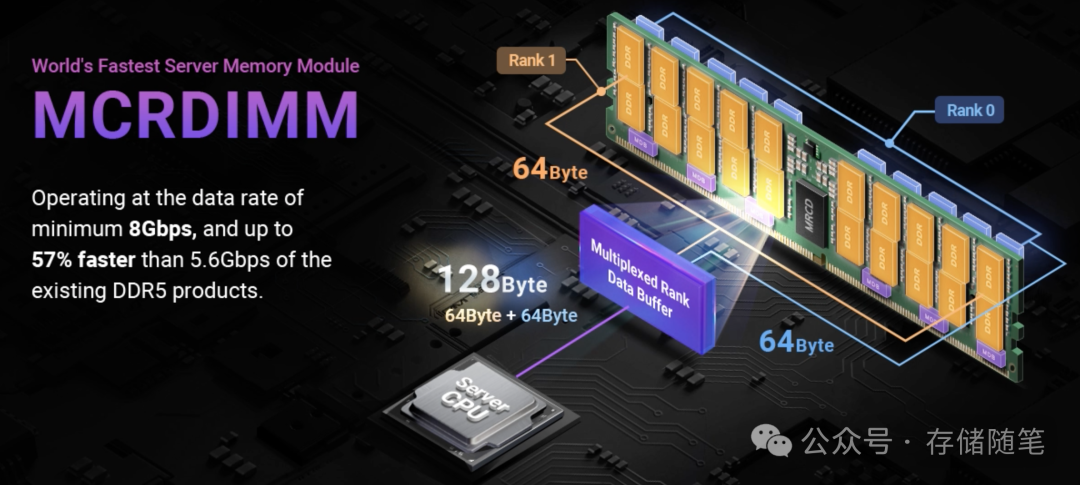

MRDIMM设计的初衷是通过现有的DDR5 DIMM技术实现带宽翻倍。与标准的DDR5 DIMM相比,MRDIMM采用创新的方法,通过组合两个DDR5内存模块,以双倍的数据速率向主机提供数据。重要的是,这种设计允许同时访问两个内存排名,因此,如果两个DDR5 DIMM各自运行在4,400 MT/s,通过MRDIMM技术整合后,输出的数据传输速率可达到8,800 MT/s。这一过程依赖于一种特殊的数据缓冲器或复用器,将两个DDR转换为单个QDR。

MRDIMM规格及发展路线图

- 第一代MRDIMM:数据传输率8,800 MT/s

- 第二代MRDIMM:数据传输率提升至12,800 MT/s

- 第三代MRDIMM:最终目标为17,600 MT/s

虽然第一代产品即将成为现实,但第三代MRDIMM的出现预计要等到2030年之后,显示了该技术长期且逐步演进的特性。

MCR DIMM的核心在于其创新的数据缓冲器(data buffer)设计,这是基于英特尔MCR技术的一种新型内存架构。传统上,DRAM模块在每次访问时只能激活一个内存列,而MCR DIMM通过在模块上集成的数据缓冲器,能够同时操作两个内存列,从而使得每次数据传输量翻倍,达到128字节。这一设计极大地提高了内存带宽,特别是在那些需要频繁读写大量数据的应用场景下,如AI推理、高性能计算和大规模数据分析等。

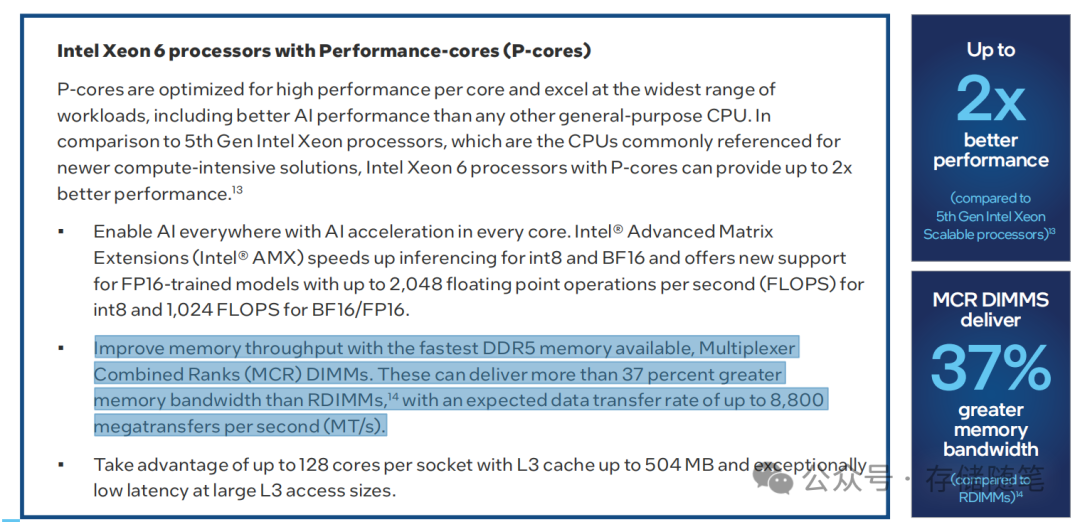

最新的英特尔Xeon 6处理器家族中,特别强调了与MCR DIMM的兼容性,旨在进一步提升数据中心的处理能力和能效。特别是针对P-core优化的处理器,MCR DIMM能够发挥其最大的性能潜力。根据Intel Xeon至强6 AP处理器数据显示,MCR DIMM相较于传统DDR5 6400MT/s RDIMM,能够提供超过37%的额外内存带宽,数据传输率最高可达8,800MT/s,这使得它成为处理大数据集和高密度计算任务的理想选择。

SK海力士作为MCR DIMM技术的主要开发者之一,已经成功开发出了全球最快的服务器内存模组样品,实现了8Gbps的数据传输速率,为业界树立了新的标杆。该技术的成功标志着内存行业在提高服务器性能和效率方面迈出了重要一步。

随着MCR DIMM技术的成熟和市场接受度的提高,越来越多的服务器制造商和云服务提供商开始将其纳入下一代产品设计中。它不仅适用于AI和HPC领域,也被视为支持云原生微服务、数据库存储和边缘计算等应用的关键技术。未来,随着技术的持续演进和标准化进程的推进,MCR DIMM有望成为高端服务器和数据中心的标准配置,引领存储技术的新一轮变革。

MCR DIMM技术的发展标志着内存解决方案正朝着更高性能、更高效率的方向快速发展。通过解决传统内存架构的带宽瓶颈,MCR DIMM为数据中心的算力提升提供了新的可能性。随着技术的不断成熟和市场的广泛接纳,MCR DIMM有望成为推动未来云计算、AI和HPC等领域发展的关键技术之一,为数字化转型注入强大动力。

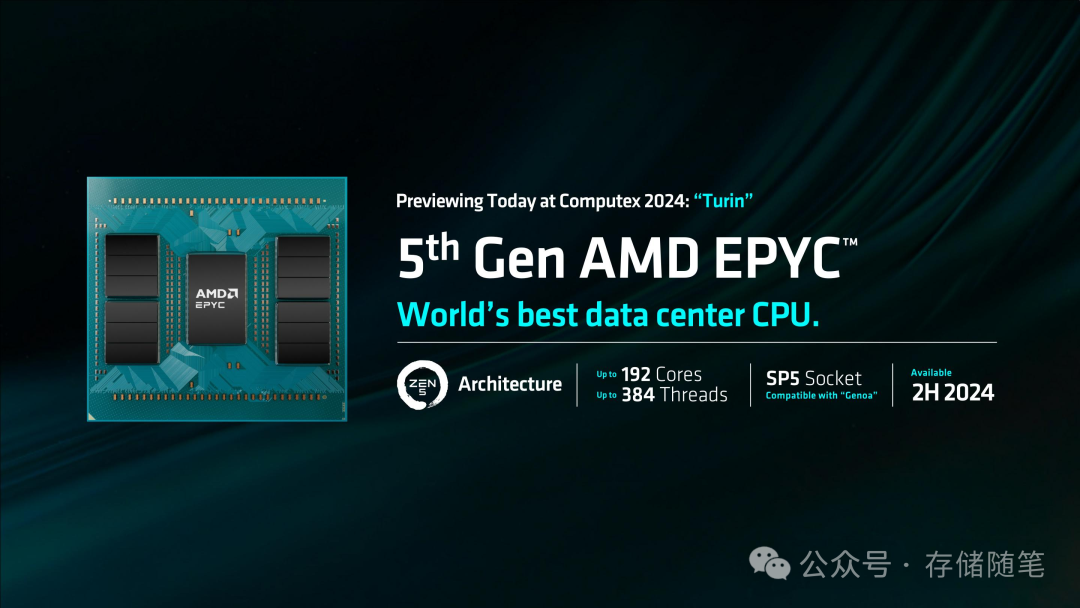

考虑到Intel的Granite Rapids(P-Core)和AMD的EPYC Turin(基于Zen 5架构)处理器预计将在2024年下半年推出,且已知Granite Rapids能够支持MCR DIMM,可以合理推测MCR或MRDIMM技术将在2024年下半年进入市场。

MRDIMM技术不仅代表了DDR5内存技术的一个重大飞跃,也是对数据中心和高性能计算领域内存带宽需求增长的直接回应。随着相关技术的成熟和处理器平台的支持,我们有望在不久的将来见证数据中心内存性能的显著提升。

如果您看完有所受益,欢迎点击文章底部左下角“关注”并点击“分享”、“在看”,非常感谢!

精彩推荐:

- 浅析MPS对PCIe系统稳定性的影响

- DPU:值不值得托付下一代存储加速架构?

- 论文解读|数据中心内存RAS技术全景剖析

- 硬盘HDD:AI时代的战略金矿?

- 断电的固态硬盘数据能放多久?

- CXL-GPU: 全球首款实现百ns以内的低延迟CXL解决方案

- 万字长文|下一代系统内存数据加速接口SDXI解读

- 数据中心:AI范式下的内存挑战与机遇

- WDC西部数据闪存业务救赎之路,会成功吗?

- 属于PCIe 7.0的那道光来了~

- 深度剖析:AI存储架构的挑战与解决方案

- 浅析英伟达GPU NCCL P2P与共享内存

- 3D NAND原厂:哪家芯片存储效率更高?

- 大厂阿里、字节、腾讯都在关注这个事情!

- 磁带存储:“不老的传说”依然在继续

- 浅析3D NAND多层架构的可靠性问题

- SSD LDPC软错误探测方案解读

- 关于SSD LDPC纠错能力的基础探究

- 存储系统如何规避数据静默错误?

- PCIe P2P DMA全景解读

- 深度解读NVMe计算存储协议

- 浅析不同NAND架构的差异与影响

- SSD基础架构与NAND IO并发问题探讨

- 字节跳动ZNS SSD应用案例解析

- CXL崛起:2024启航,2025年开启新时代

- NVMe SSD:ZNS与FDP对决,你选谁?

- 浅析PCI配置空间

- 浅析PCIe系统性能

- 存储随笔《NVMe专题》大合集及PDF版正式发布!

版权归原作者 古猫先生 所有, 如有侵权,请联系我们删除。