文章目录

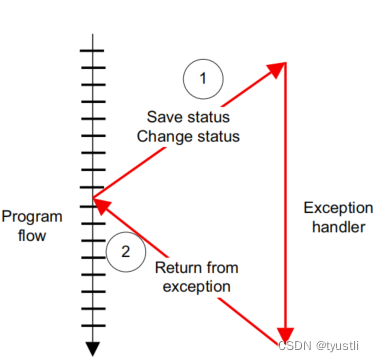

ARM 处理器对异常中断的响应过程

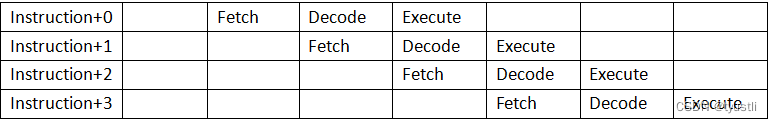

ARM 指令为三级流水线:取地,译码和执行

进入中断的时候 LR = PC -4

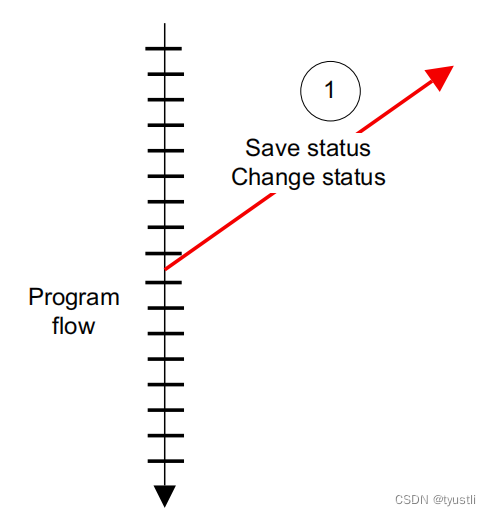

当出现异常时,ARM 内核自动执行以下操作

- 将 cpsr 寄存器的值保存到 spsr_mode 寄存器中,备份寄存器指明了当前处理器的操作模式

- 将程序返回地址存放在 lr_mode 寄存器中

- 将CPSR模式位修改为与异常类型相关联的模式 - CPSR 寄存器的其他位取决于 CP115 控制寄存器设置的值- T bit 位被设置为 CP15 TE bit- J bit 被清零,E bit 被设置为 EE bit

- 将 PC 指向异常向量表对应的地址

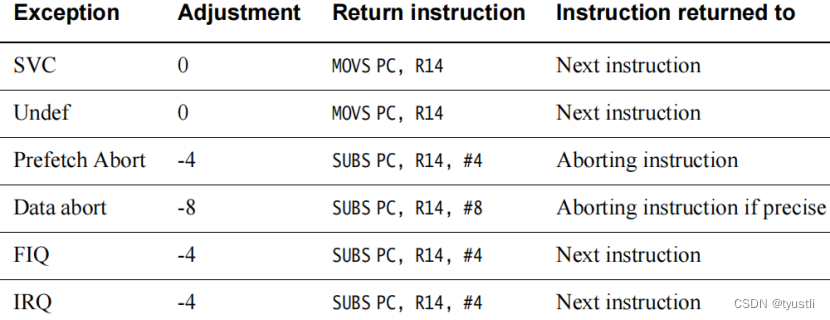

从异常中断处理程序中返回

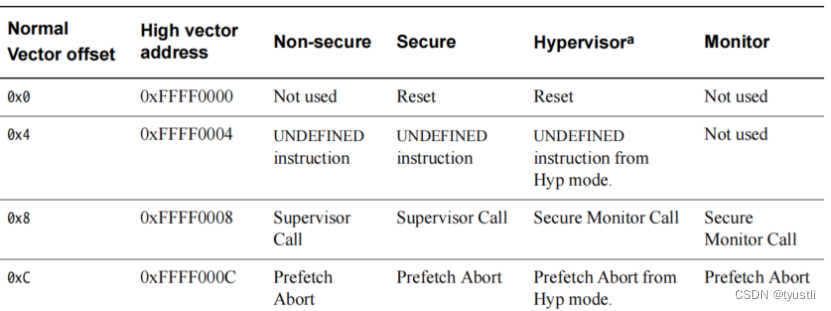

中断向量表

链接寄存器(LR)用于在异常处理后存储适当的PC 地址,当程序返回时,LR 应该做出相应的调整。

从表中可以看到 ARM 共有 7 中异常,其中断向量表如下:

ldr pc,=Reset_Handler /* Reset */

ldr pc,=Undefined_Handler /* Undefined instructions */

ldr pc,=SVC_Handler /* Supervisor Call */

ldr pc,=PrefAbort_Handler /* Prefetch abort */

ldr pc,=DataAbort_Handler /* Data abort */.word 0/* RESERVED */

ldr pc,=IRQ_Handler /* IRQ interrupt */

ldr pc,=FIQ_Handler /* FIQ interrupt */

异常程序返回有两个事情要做:

- 从 spsr_mode 寄存器中恢复 cpsr 寄存器

- 将程序返回地址写到 pc 寄存器

版权归原作者 tyustli 所有, 如有侵权,请联系我们删除。