文章目录

AHBRAM模块验证笔记

AHBRAM模块解读

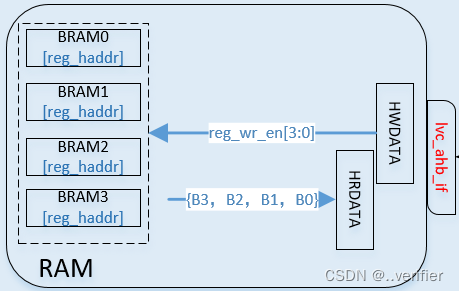

AHBRAM是一个以AHB协议通信的RAM存储模块。RAM内部含有4块BRAM模块,每块BRAM均能存储8bit的数据,存储空间为16KB,整块RAM存储空间为64KB。通过AHB协议对RAM进行写操作时,根据接口上传输位宽和传输地址逻辑判断后,使能对应的BRAM块,并存入数据;通过AHB协议对RAM进行读操作时,根据接口上传输地址,对4个BRAM模块相应地址的数据进行拼接并读出。

其中,通信协议AHB采用了简化版:

1、只有一个master和一个slave,hgrant = 1;

2、模块预置条件:每次传输均正确且传输完成,hready = 1,hresp = okay;

3、单时钟沿变化;

4、支持burst传输,但只考虑single传输,即hburst = single,htrans = idle / Nonseq两种状态;

5、burst传输支持最大位宽为32bit。

AHBRAM验证结构布局

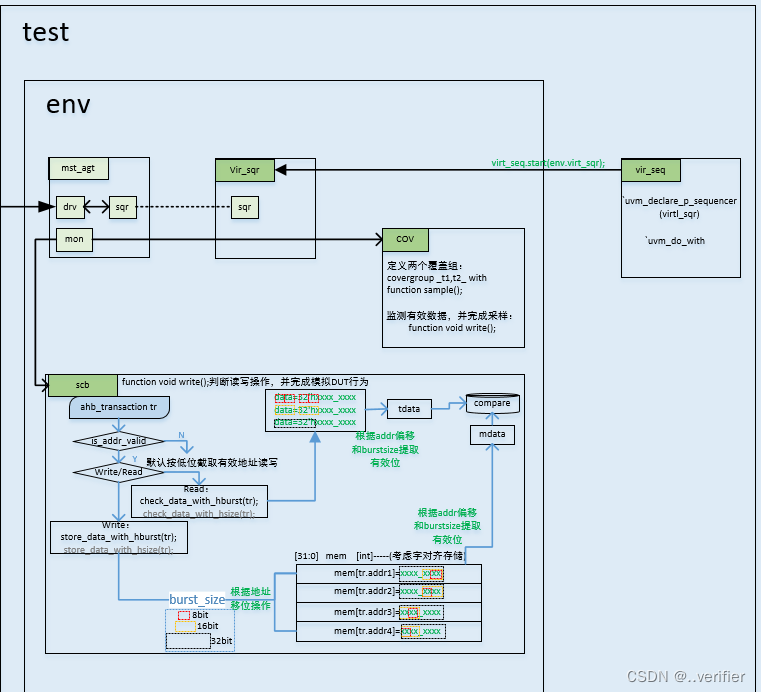

整个验证环境env中,包含了一个mst_agt,其中drv通过与之连接的TLM端口获取到挂载在sqr上的seq,并将其驱动到接口上,进而与RAM模块进行交互,而mon则将接口上监测到的数据通过其item_observed_port发送到其与之连接的端口上,比如scb和cov的anasis_imp上。scb内创建了模拟RAM行为的mem,对mon向其发送的数据进行相应的读写操作,cov则创建了2个功能覆盖组,并对相应信号进行采样。同时环境中还包含有virt_sqr,其不与任何driver进行通信,而是作为底层sqr的管理者,协调各个sqr。一旦virt_seq挂载在virt_sqr上,其就能通过p_sqr拿到各个底层的sqr句柄,进而使用·`uvm_do系列宏完成激励的创建、约束发送等。同时,virt_seq例化在test层次,更接近于用户,将激励与环境结构隔离开来,便于环境的可重用;同时在tb中,例化了AHBRAM模块,并指定地址位宽addresswith = 16。

AHBRAM测试用例

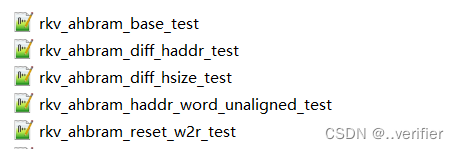

(1)base_test主要工作:

1、创建了cfg配置对象,并指定ram的有效地址范围为32‘h0~32’h0000_FFFF;

2、通过config_db#(virtual rkv_ahbram_if)::get(this, " ",“vif”,cfg.vif)获得虚接口句柄;

3、将env中cfg配置成创建的cfg后,创建整个env环境结构。

(2)其余test则继承于base_test,但在其run_phase中例化了不同的seq,且将其挂载至顶层virt_sqr,同时通过objection机制控制仿真的运行。

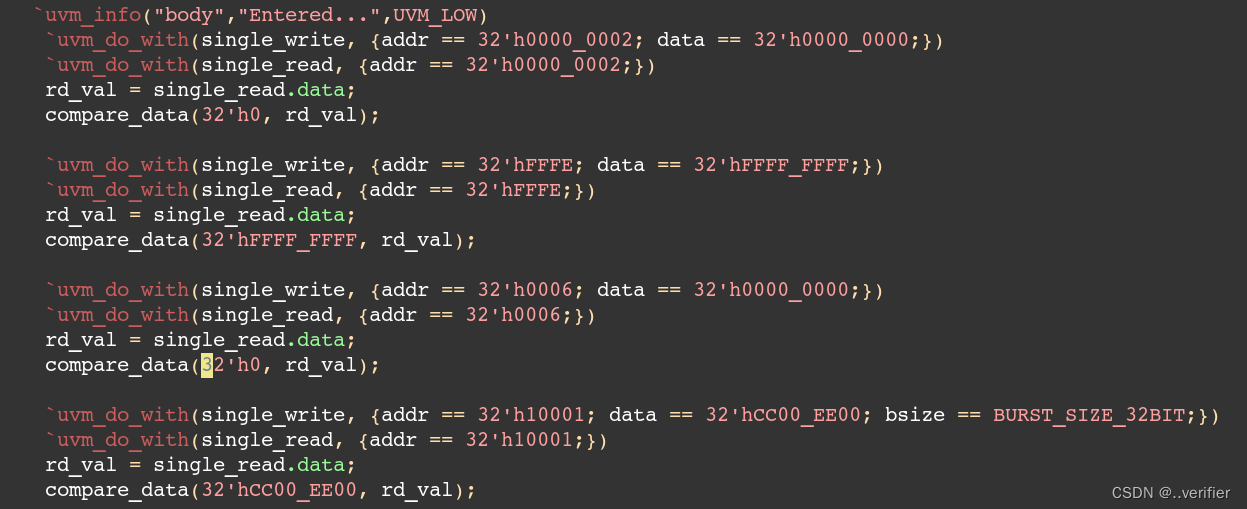

diff_haddr_test和diff_hsize_test分别针对要传输的transaction的addr和burst_size做随机约束后,通过

uvm_do_with宏完成读写测试; haddr_word_unligned_test随机约束burst_size,并规定burst_size = 16bit和32bit时,addr[1] = 0和addr[1:0] = 0(即支持字不对齐传输),通过

uvm_do_with宏完成读写测试;

reset_w2r_test则测试复位后对应addr的存储空间复位值是否为全X。

AHBRAM覆盖率收集

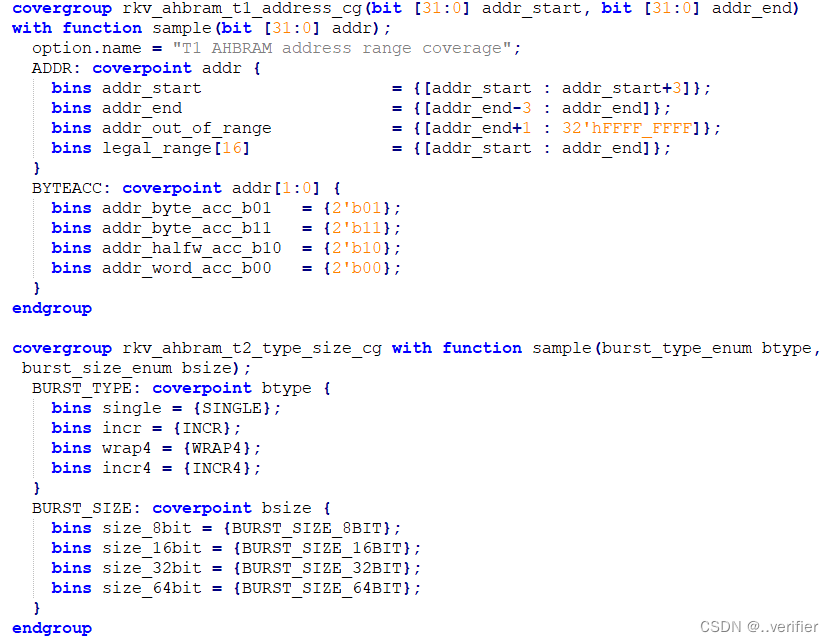

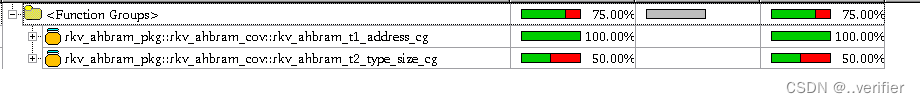

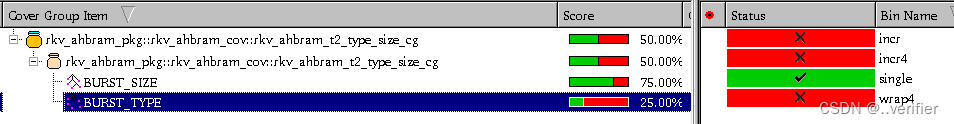

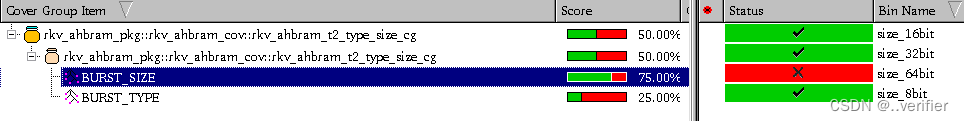

定义2个covergroup,分别关心传输地址addr和传输类型、传输位宽:

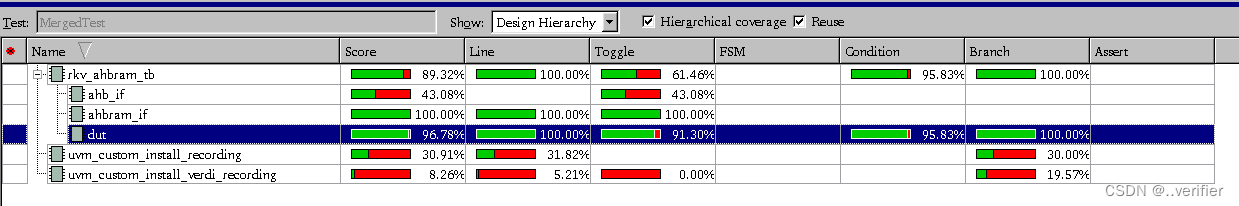

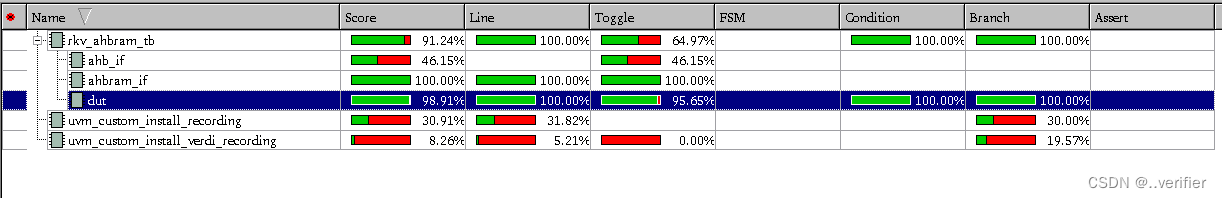

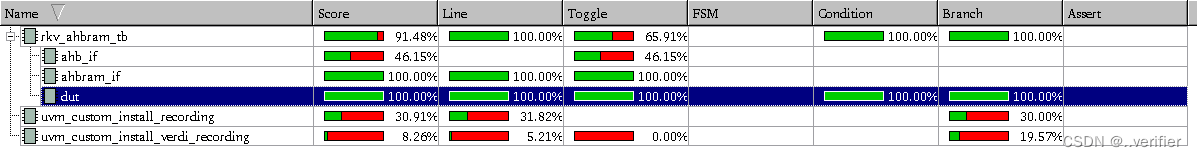

使用固定种子seed_1和随机种子分别跑以上测试,可以得到合并后的代码覆盖率情况如下:

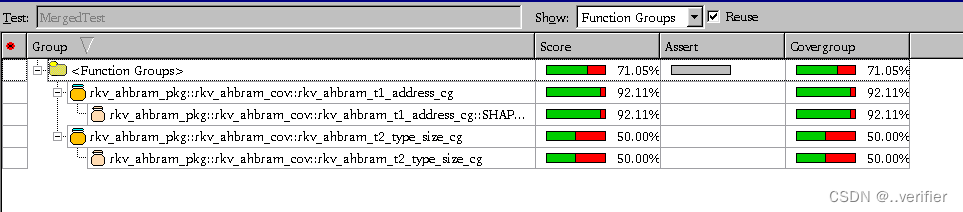

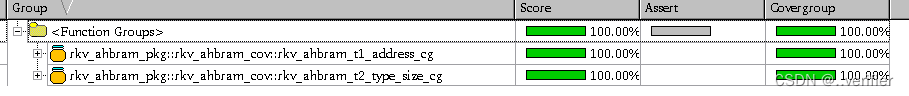

功能覆盖率情况如下:

分析覆盖率收集情况

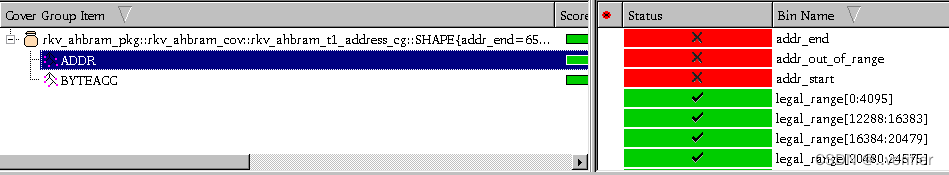

关心传输地址addr的功能覆盖组地址的边界未覆盖到,同时非法地址未覆盖到。

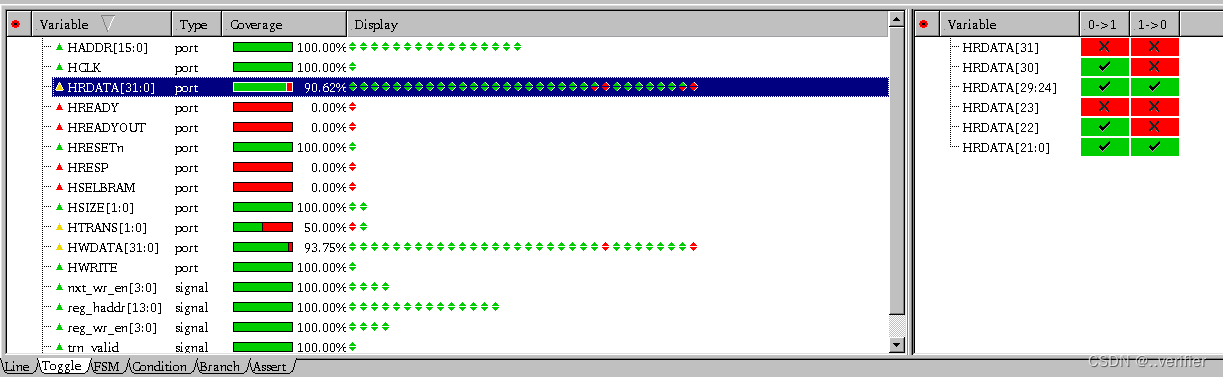

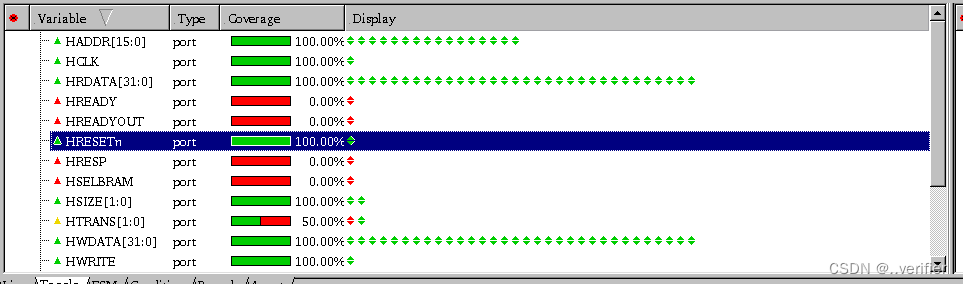

代码覆盖率中hwdata和hrdata等信号的个别bit的翻转未覆盖到。

添加新的测试用例

(1)针对合法地址边界和非法地址以及数据的bit位翻转,编写如下测试用例:

备注:非法地址读写时,会按低位截取有效地址进行读写,即能正常读写,但写入地址不是预期地址。

此时覆盖率情况如下:

此时再次分析覆盖率:

由于设计中AHBRAM不支持64bit位宽传输,同时只验证single传输,功能覆盖率对应部分可以先exclude;而hready、hreadyout恒为1,hresp=okay,且hselbram为1,代码覆盖率部分也可先exclude;可以得到最终的覆盖率情况:

异常激励测试

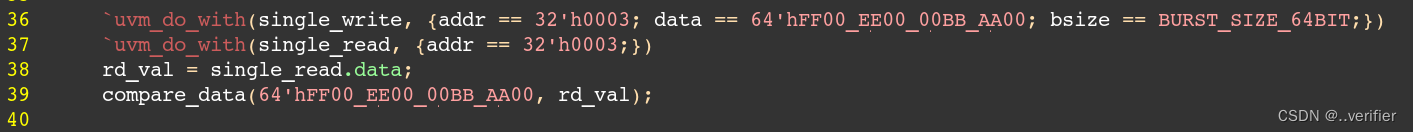

由于RAM不支持64bit位数据传输,则采用64bit位宽数据作为异常激励进行读写测试:

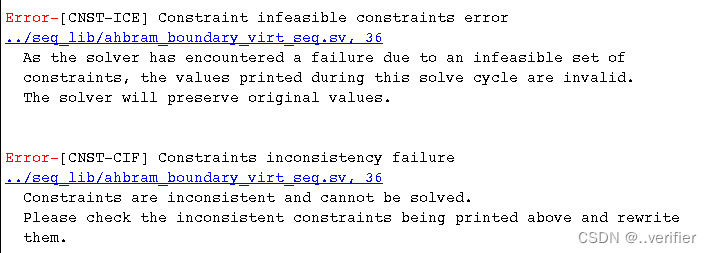

此时,DVE仿真窗口会报ERROR错误:

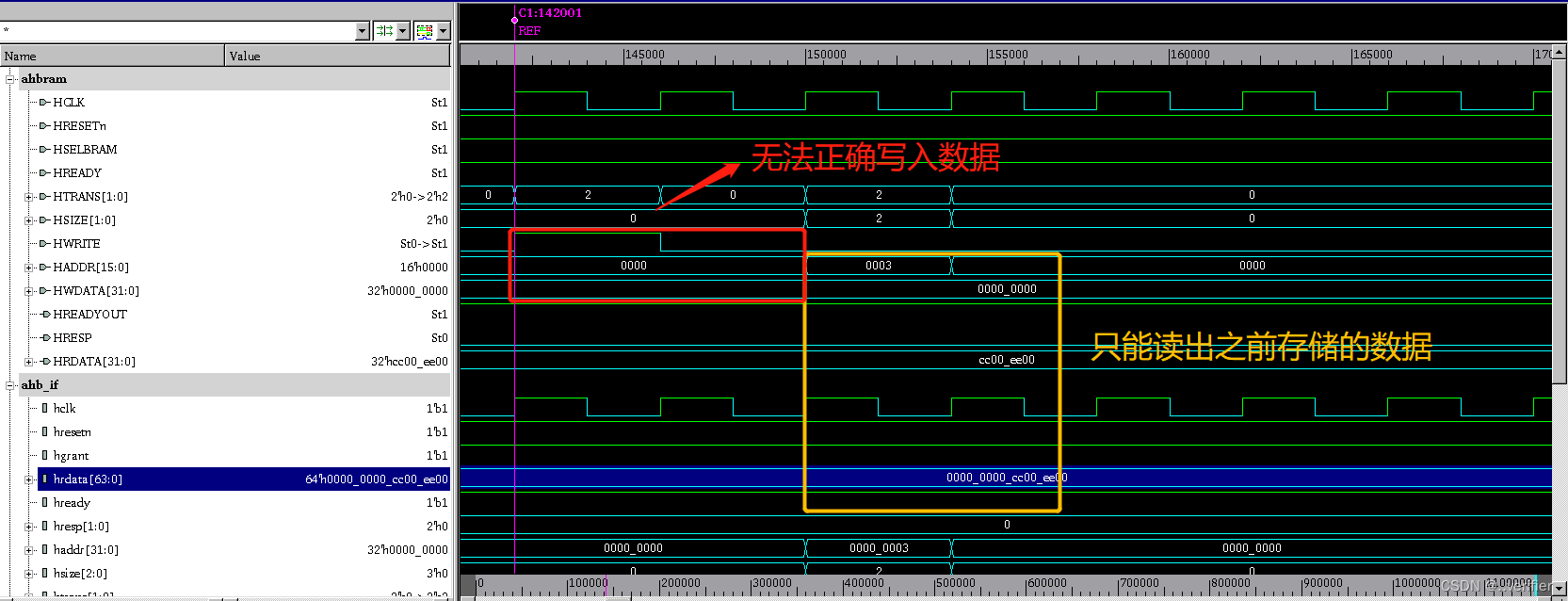

同时,RAM无法写入64bit数据,且只能读出之前对应地址存储的数据:

版权归原作者 ..verifier 所有, 如有侵权,请联系我们删除。