基于瑞芯微平台cif接口dvp相机的视频接入(ov2640、rv1126为例)

名词定义

CIF,指RK芯片中的VIP模块,用以接收Sensor数据并保存到Memory中,仅转存数据,无ISP功能

DVP,一种并行数据传输接口,即Digital Video Port

HSYNC,指DVP接口的行同步信号

PCLK,指Sensor输出Pixel Clock

VSYNC,指DVP接口的场同步信号

V4L2,即Video4Linux2,Linux kernel的视频处理模块

视频格式

视频格式一般分成BT1120(BT656)和BT601两种。

BT1120视频数据只支持内同步。信号内同步的意思是图像数据和同步信号均包含在图像数据中,通过关键字恢复同步信号。可以参考我的另一篇博客SDI视频数据流格式简介

BT601协议采用外同步,外同步是指图像数据和同步数据(HS、VS、DE)单独传送。

因为内同步是将图像与同步信号一起传送,因此会有同步分离机制,所以亮度及色彩不可能全编码,以8BIT为例,可以传送的范围为0-255,但内同步一起传送,实际编码不可能有256范围,在ITU-656中大多采用16-235,而ITU-601因为采用外同步,可以传送0-255 范围的数据。因此,内同步的色采及亮度在细节上没有内同步好。但是,在串行编码及低带宽传送中,内同步可以减少数据流,因此,通过内同步传送图像虽然色彩有一定的损失,但可以换来更低的带宽。

视频格式一般在视频的驱动程序中进行设置,只有以下两种格式:

config->type = V4L2_MBUS_BT656;//BT1120 BT656

config->type = V4L2_MBUS_PARALLEL;//BT601

一般BT601使用较多,外同步信号,需要配合行场同步信号。

sensor与isp

sensor与isp之间的关系图一般如下所示:

首先ISP也就是ARM芯片端,需要通过I2C总线对sensor进行配置,主要通过SCL(时钟线)和SDA(数据线)对sensor的寄存器进行配置,可以决定sensor的分辨率、输出视频格式(rgb、yuv)、白平衡等进行设置。

部分摄像头可能不含晶振,比如OV7670,所以就需要ISP提供相机时钟,也就是XCLK进行驱动,一般在24MHz左右。部分带有晶振的相机,比如OV2640,由于集成了晶振,所以无需进行外部时钟驱动。

VS、HS和PCLK是sensor输出的行场同步信号和像素时钟。

DATA是sensor输出的像素值,一般8位较多。

然后对以上的各个部分进行介绍。

I2C

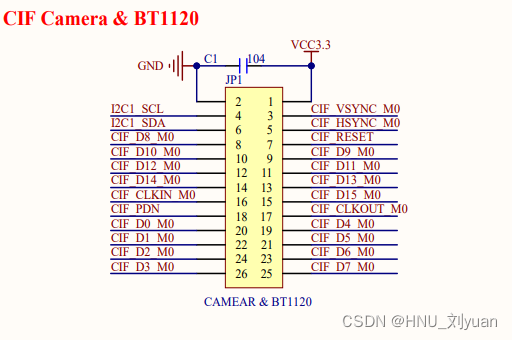

由于ARM芯片具有较多的I2C引脚,比如RV1126好像就有5个I2C引脚。每一个相机的I2C都要连接到对应的引脚上,以正点原子的RV1126开发板为例,I2C就挂载到了I2C1下:

在设备树dts中,就要把OV2640的摄像头节点放在I2C1下,比如:

&i2c1 {

status ="okay";

clock-frequency =<100000>;

ov2640: camera@3c {

compatible ="ovti,ov2640";

pinctrl-names ="default";

reg =<0x3c>;......}}

摄像头所支持的I2C时钟速度最快可达到400Kbps,同时每一款摄像头都有专属的地址,比如ov2640的地址是0x3c,注意地址是硬件设计死的无法更改。

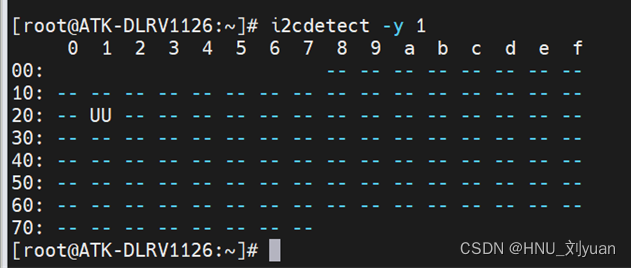

I2C设备可以使用i2cdetect工具进行调试,比如查看i2c1下挂载了哪些设备,可以通过以下命令进行查看:

i2cdetect -y 1

若我在0x21处挂载了设备,将得到:

同时可以使用以下命令查看i2c寄存器中的值,比如我要查看i2c1下地址为0x3c处寄存器的值,可以通过以下名称查看:

i2cdump -y -f 1 0x3c

值得注意的是有些摄像头将power_down拉低后,开发板才能够通过i2c与相机寄存器之间进行通信,比如上方为拉低了的,下方为未拉低。

另:OV公司的I2C不是标准的I2C总线,为了避开专利,他们采用的是SCCB总线技术,不过经过测试与I2C区别不大。

SCCB是欧姆尼图像技术公司(OmniVision)开发的一种总线,应用于OV系列图像传感器上。SCCB最主要是阉割了IIC的连续读写的功能,即每读写完一个字节就主机必须发送一个NA信号。

XCLK

部分不带晶振的摄像头需要提供XCLK像素时钟进行驱动,在设备树中可以通过以下进行添加,注意时钟名字要与驱动对应:

比如设备树中可能如下:

clocks =<&cru CLK_CIF_OUT>;

clock-names ="xvclk";

驱动部分对应如下:

priv->clk = v4l2_clk_get(&client->dev, "xvclk");if(IS_ERR(priv->clk))return -EPROBE_DEFER;

行场同步信号

不同相机的行场同步信号可能不同,具体可以查询芯片手册,不过注意的是芯片手册不一定准确,比如OV2640,芯片手册的时序为:

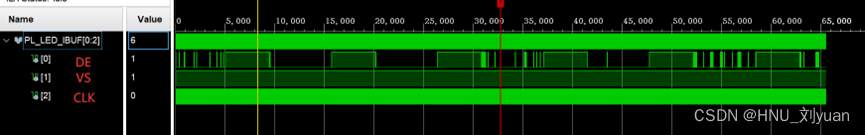

可以看出是标准的SDI格式,也就是当DE也就是HREF为高时,VSYNC为低,VSYNC只在有效像素前产生一段高电平。但是按照这个时序产生的同步信号始终无法抓取到图像,经过抓取之后发现OV2640输出的时序如下:

可以看出当DE为高时,也就是有效像素部分,VS也为高,基本与手册中写的相反,按照上面的时序即可抓取到图像。

正确OV2640时序的Verilog代码如下,注意分辨率为800x600,YUYV格式8bit:

parameter ROWS =600;

parameter COLS =1600;

parameter ROWS_TOTAL =672;

parameter COLS_TOTAL =3840;

parameter ROW_START =36;

parameter COL_START =1000;

reg [12:0] rROW;

reg [12:0] rCOL;

always@(posedge wCLK18M)

begin

if(!iRst)

begin

rROW <=0;

rCOL <=0;

end

else

begin

if(rCOL==COLS_TOTAL-1)

begin

rCOL <=0;

rROW <= rROW + 1;

end

else

begin

rCOL <= rCOL + 1;

end

if(rROW == ROWS_TOTAL)

begin

rROW <=0;

end

end

end

reg r2640DE;

reg r2640VS;

reg [7:0] r2640H;

always@(posedge wCLK18M)

begin

if(rROW >= ROW_START && rROW <(ROW_START + ROWS))

begin

r2640VS <=1;

if(rCOL >= COL_START && rCOL <(COL_START + COLS))

begin

r2640DE <=1;

end

else

begin

r2640DE <=0;

end

end

else

begin

r2640VS <=0;

end

end

生成的波形如下:

同时也要注意HS和VS的极性,也就是有效时的电平高低,主要收到设备树和驱动的控制,设备树部分如下:

&i2c1 {

status ="okay";

// clock-frequency =<400000>;

clock-frequency =<100000>;

ov2640: camera@3c {

compatible ="ovti,ov2640";

pinctrl-names ="default";

pinctrl-0 =<&cifm1_dvp_ctl>;

reg =<0x3c>;

clocks =<&cru CLK_CIF_OUT>;

clock-names ="xvclk";

port {

/* Parallel bus endpoint */

cam_para_out1: endpoint {

remote-endpoint =<&cif_para_in>;

bus-width =<8>;

//data-shift =<2>; /* lines 9:2 are used */

hsync-active =<1>;

vsync-active =<1>;//<1>;

pclk-sample =<1>;};};};};&rkcif_dvp {

status ="okay";

port {

cif_para_in: endpoint {

remote-endpoint =<&cam_para_out1>;

bus-width =<8>;

hsync-active =<1>;

vsync-active =<1>;};};};

驱动部分:

config->flags = V4L2_MBUS_PCLK_SAMPLE_RISING | V4L2_MBUS_MASTER |

V4L2_MBUS_VSYNC_ACTIVE_HIGH | V4L2_MBUS_HSYNC_ACTIVE_HIGH |

V4L2_MBUS_DATA_ACTIVE_HIGH;

两者要与实际情况相匹配。

DATA

sensor输出的数据一般8位居多,也有16位和10位的,RV1126的CIF接口输入如下:

优先使用CIF接口的高位进行传输。

同时还要对MEDIA_BUS_FMT进行配置,与sensor输出的像素格式对应,可以参考V4L2的手册,格式十分丰富。

以OV2640为例支持以下的格式:

static u32 ov2640_codes[]={

MEDIA_BUS_FMT_YUYV8_2X8,

MEDIA_BUS_FMT_UYVY8_2X8,

MEDIA_BUS_FMT_YVYU8_2X8,

MEDIA_BUS_FMT_VYUY8_2X8,

MEDIA_BUS_FMT_RGB565_2X8_BE,

MEDIA_BUS_FMT_RGB565_2X8_LE,

};

以MEDIA_BUS_FMT_YUYV8_2X8为例,视频输出的格式位YUYV,并且深度是8bit色深,每次只传输8bit,两个像素周期才是一个完整的像素。

抓图

抓图一般使用v4l2-ctl进行抓图,对于dvp接口可以在video0进行抓图,对于mipi则不行,抓图实例如下:

v4l2-ctl -d /dev/video0 --set-fmt-video=width=800,height=600,pixelformat=YUYV8_2X8--stream-mmap=3 --stream-skip=3 --stream-to=./cif.out --stream-count=1 --stream-poll

抓图成功一般如下所示,会有 < 打印输出:

并且对于800x600大小YUYV8_2X8格式的图片一般占用940k存储空间。

并且可以通过以下python代码查看像素值:

yuv ="./pic.out"

with open(yuv, "rb") as yuv_f:

yuv_bytes = yuv_f.read()

yuv_data = np.frombuffer(yuv_bytes, np.uint8)

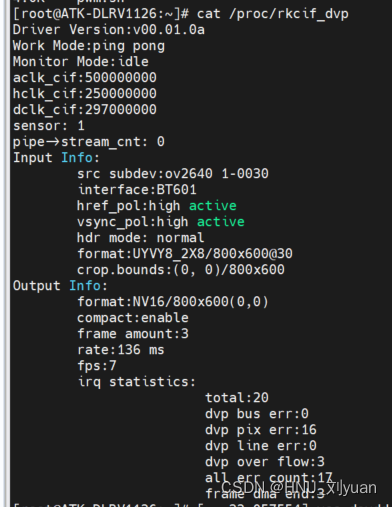

同时在/proc路径下也会有统计信息得到保存,通过以下命令进行查看:

cat /proc/rkcif_dvp

以上就是对dvp相机的视频接入的简单介绍,各位有疑问可以留言,进行交流。

版权归原作者 HNU_刘yuan 所有, 如有侵权,请联系我们删除。