文章目录

前言

在上计算机组成原理研讨课时,需要用到verilog写电路图。之前在数字电路课,老师已经提供了相应的软件和环境配置。但由于当时小编因为期末大作业破大防(痛苦面具.jpg),把全部内容都删掉了,因此还需要重新配置环境。

由于小编专业并非硬件方向,同时觉得之前使用很专业的软件时比较复杂(有点丑陋hhh),因此这次选择使用万能的VScode + 插件来写(方便之后删掉bushi )。废话到这,开始正文。

一、需要的配置软件

- iverilog

- ctags.exe

官方网址:

iverilog: iverilog下载地址

ctags: ctags下载地址

二、使用步骤

1.安装iverilog

- 选择一个比较干净的位置安装iverilog(路径最好不要包含中文,防止奇奇怪怪的问题产生)。

- 点击.exe文件,进行安装。注意:安装过程中最好将所有选项都勾选上,防止后面出错

2.配置环境变量

将安装好的iverilog及其自带的gtkwave添加到系统环境变量中。

- 系统搜索编辑系统环境变量

- 点击环境变量

- 点击新建

- 将文件夹iverilog\bin的绝对路径和iverilog\gtkwave\bin的绝对路径分别添加至系统环境变量中

3.安装VScode插件

在插件商店里找到一下几个红框内插件并安装(插件图标为左侧四个小方块)

4.对插件进行配置

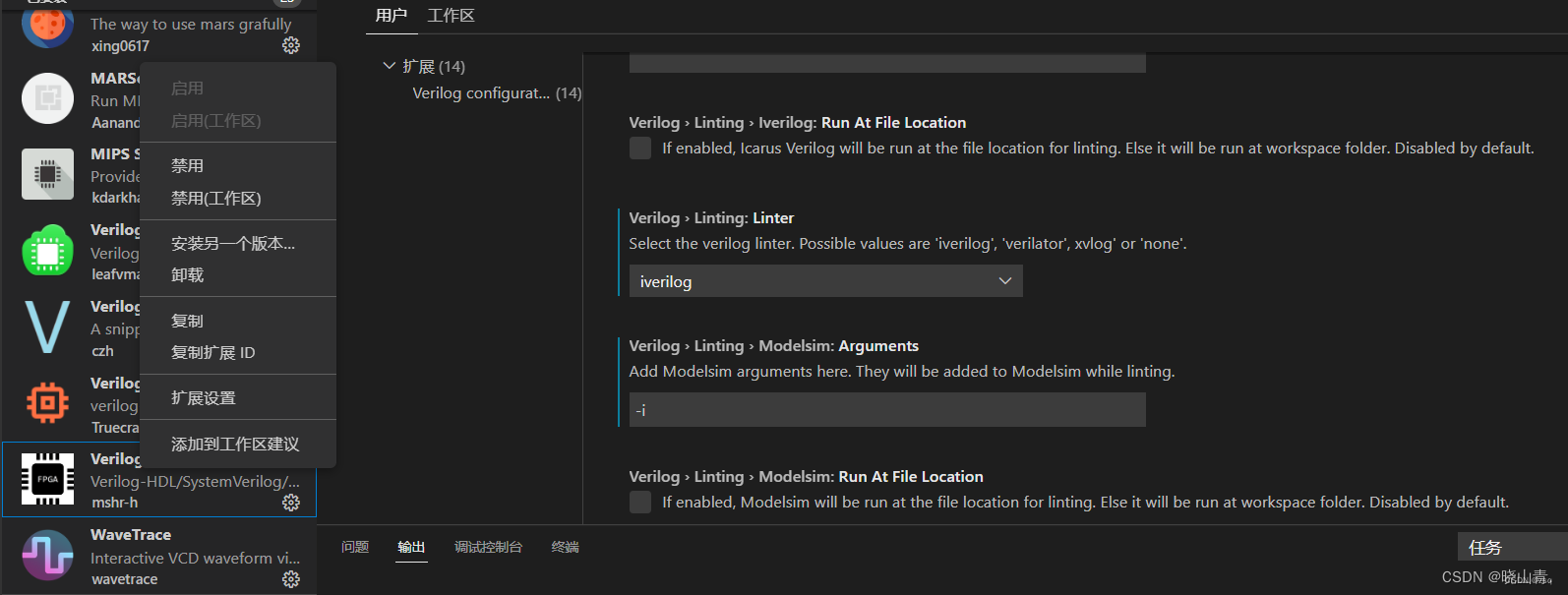

- 右键选择Verilog-HDL/SystemVerilog/Bluespec SystemVerilog(即上图中黑白配色的插件,第四个)

- 点击扩展设置

Verilog › Ctags: Path:填入ctags.exe文件的绝对路径

Verilog › Linting: Linter:选择iverilog

Verilog › Linting › Modelsim: Arguments:填入**-i**

重启之后,你就会发现你的Vscode支持verilog代码补全,代码高亮,报错,以及编译的功能

5.插件的使用

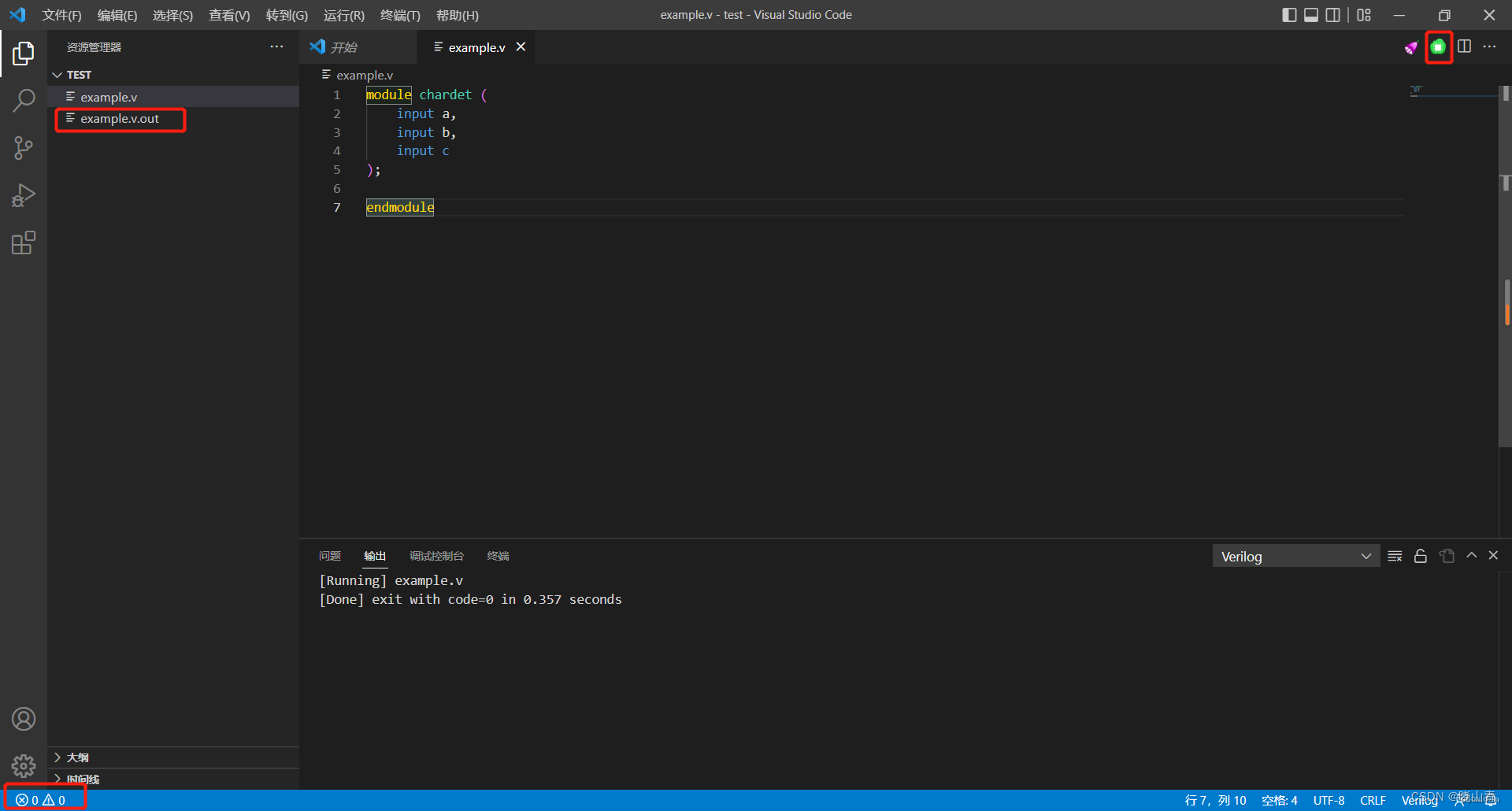

- verilog文件后缀为

.v,点击右上角的绿色的编译按钮,若无错误提醒,即可编译成功,并在左侧的文件管理窗口看见.v.out的文件

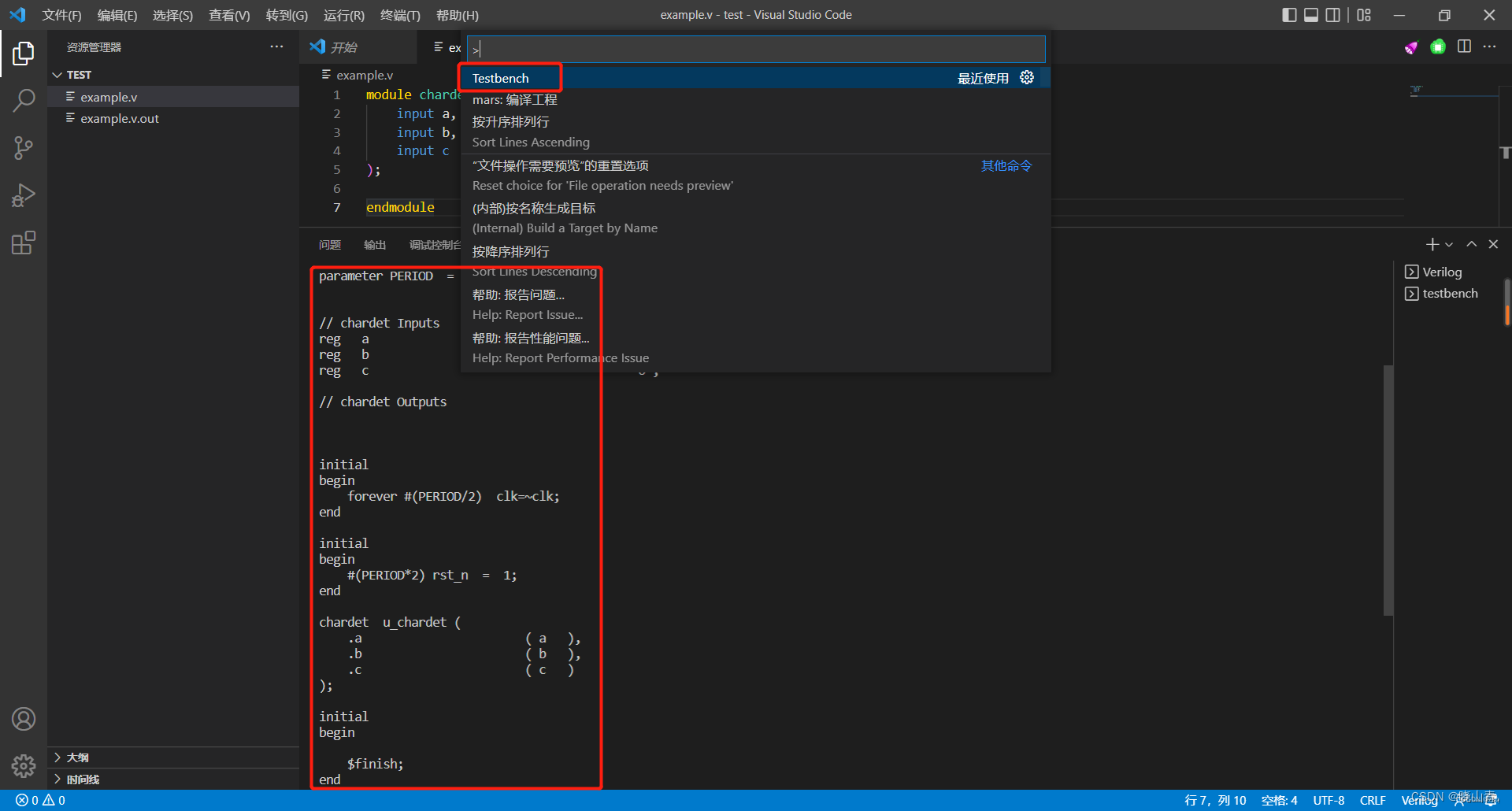

- 生成Testbench模板 在VScode使用快捷键Ctrl+Shift+P打开功能键,输入或者选择Testbench,运行,即可在终端中显示生成的模板文件,复制内容生成tb文件即可,但要注意的是文件后缀仍然是

.v

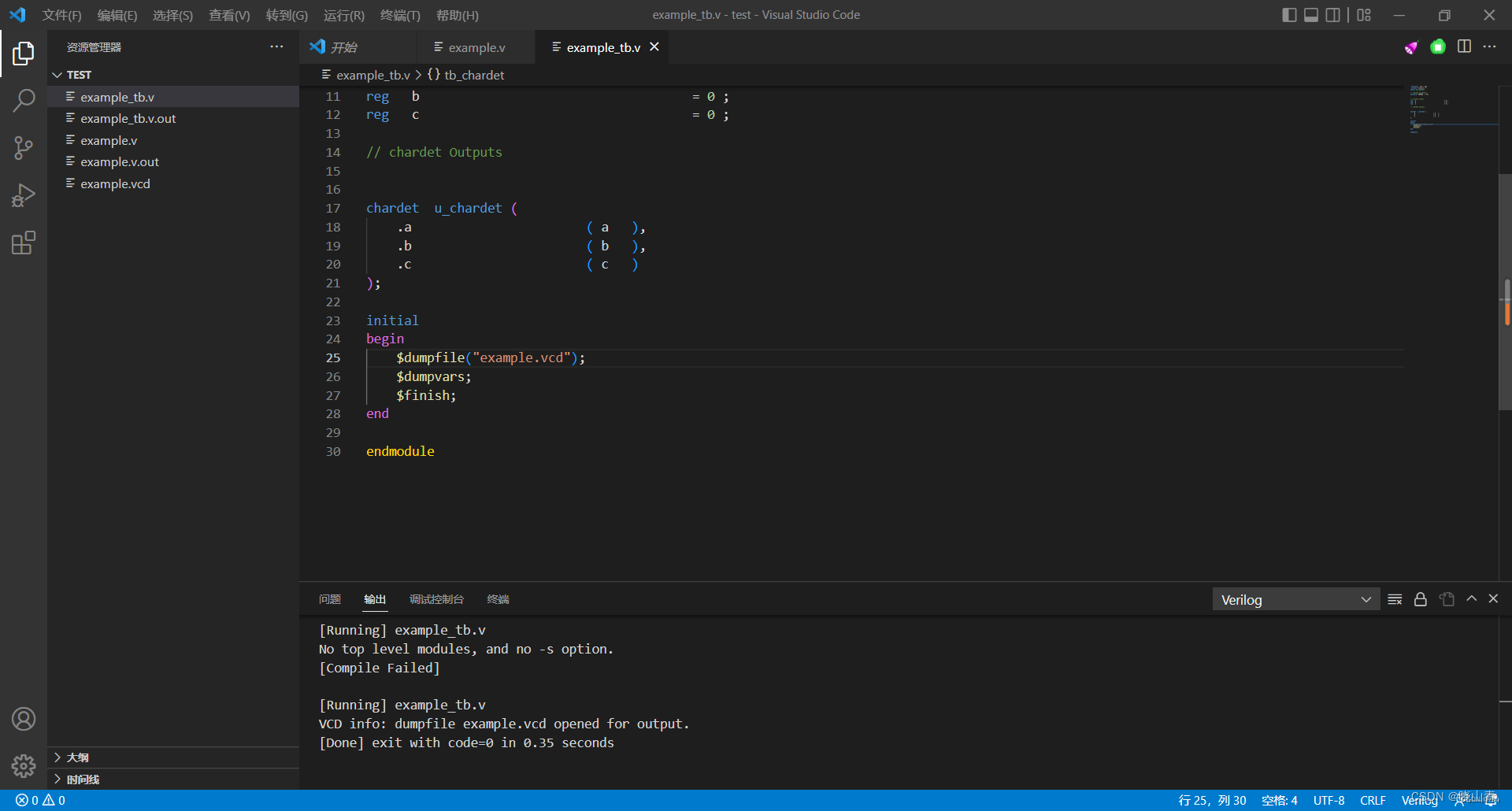

- 对自动生成的testbench进行改编 根据要测试的文件的内容,改写testbench。同时在testbench文件开头添加一下代码以引用待测文件````include "[文件名.v]"

同时,在initial块中加入如下代码以生成波形文件:$dumpfile("波形文件名.vcd");$dumpvars;其中$dumpfile指定波形文件名,$dumpvars表示所有定义的wire和reg都参与仿真。 再自行设置测试数据(在dumpvars和finish的中间添加状态代码)后点击运行,即可发现tb文件的.v.out文件,同时还有vcd```文件。

- 观察仿真波形 打开

vcd文件,点击添加信号,即可查看波形。

总结

以上就是全部内容,本文仅仅简单介绍了如何使用VScode和插件编译并运行verilog代码并生成仿真波形,后续的遇到的问题会加以补充。

特别鸣谢,@晓山青. 的文章VScode配置verilog环境,本文内容参考上述文章。

版权归原作者 zsq 所有, 如有侵权,请联系我们删除。