VScode 配置verilog环境

在win11的系统里,ise软件不能运行,而在虚拟机中ise的配置也很费劲,今天在这里教大家在VScode中玩转Verilog。

实现代码补全、代码高亮、错误检查

实现生成Testbench

实现波形仿真

所需配置文件

iverilog(自带gtkwave)、ctags.exe

所需配置文件

官方下载网址(速度较慢)

iverilog:Icarus Verilog for Windows (bleyer.org)

ctags:发布 ·通用-雄鹿/雄鹿-win32 ·GitHub

特别注意:

在安装iverilog时对于安装中的所有选项都勾选,避免出现其它问题。

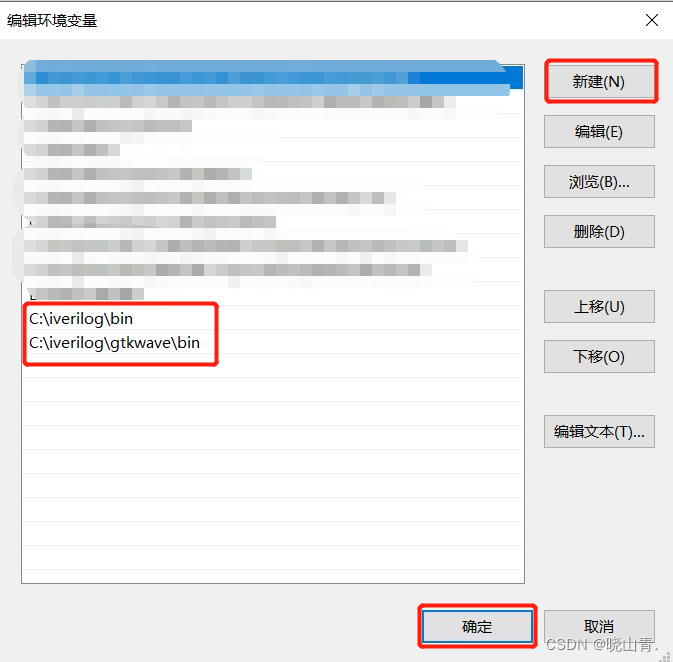

环境变量配置

将iverilog文件夹中的bin文件夹以及iverilog文件夹中的gtkwave文件夹中的bin文件夹的路径添加到系统环境变量中

系统环境变量:系统属性-高级环境变量-系统变量-Path

双击打开Path,点击新建,分别输入两个bin地址,点击确定。

确认成功之后在运行框中分别输入

iverilog -v

和

gtkwave -v

,如果有正常输出即为设置成功。

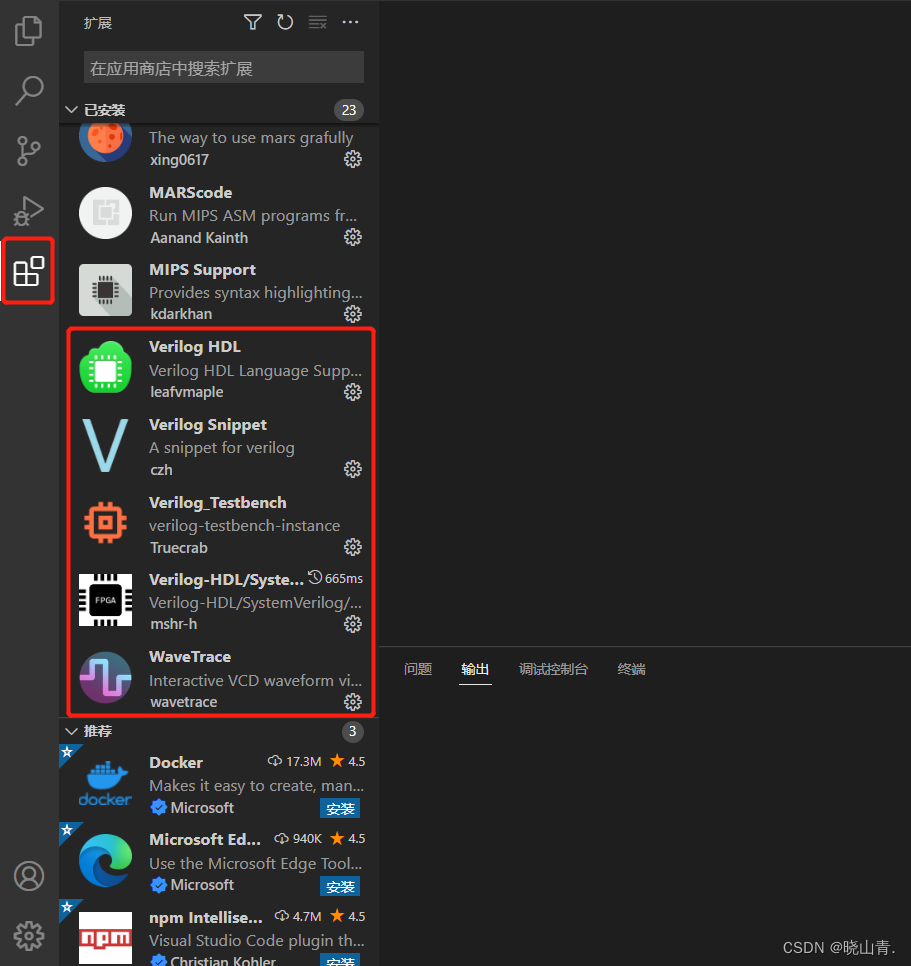

安装VScode插件

在VScode的拓展里安装如下五个插件,以支持Verilog功能

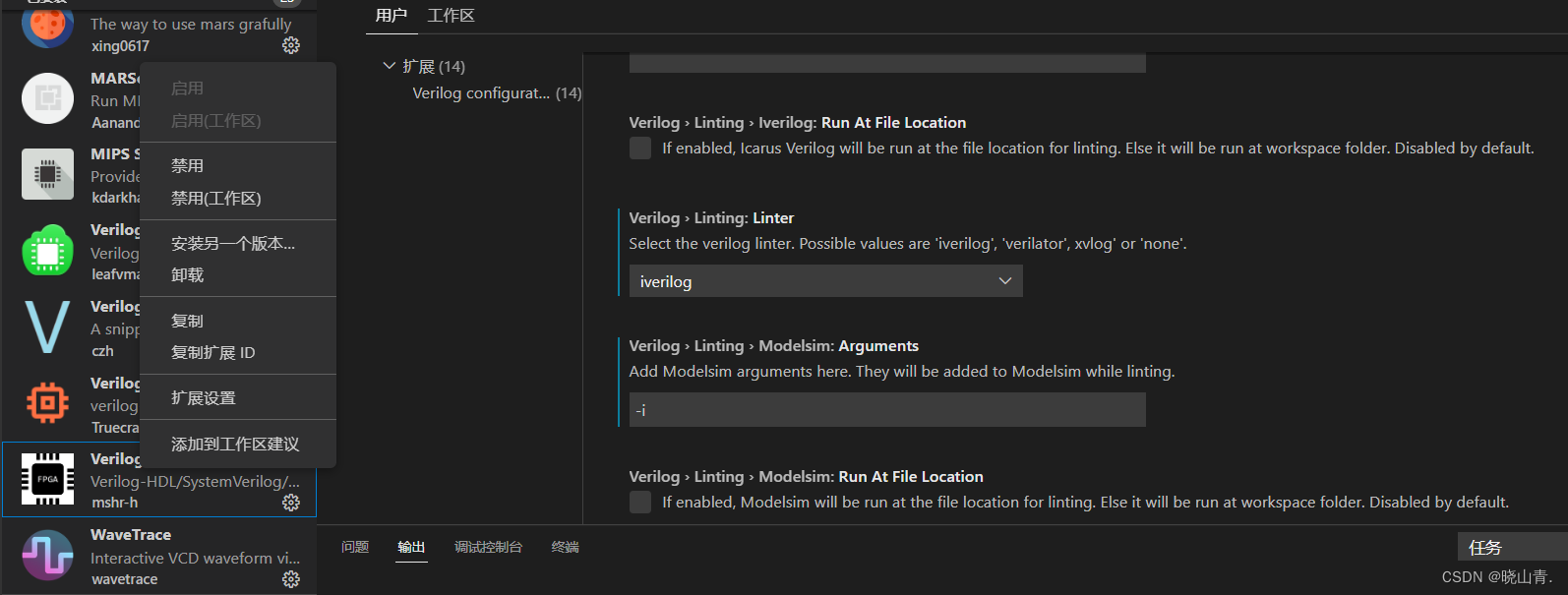

同时我们需要对于Verilog-HDL插件进行配置

右键Verilog-HDL -选择拓展设置

Verilog › Ctags: Path:填入ctags.exe文件的绝对路径

Verilog › Linting: Linter:选择iverilog

Verilog › Linting › Modelsim: Arguments:填入**-i**

重启之后,你就会发现你的Vscode支持verilog代码补全,代码高亮,报错,以及编译的功能

为了之后testbench测试文件的自动生成,我们需要在VScode的终端中分别输入以下代码,搭建所需要环境(前提是已安装Python环境,这个可以在Baidu上自行学习)

pip install certifi

pip install chardet

pip install idna

pip install urllib3

插件的使用

编译

在文件夹中打开

.v

的verilog文件,点击右上角的编译按钮,若无错误提醒,即可编译成功,并在左侧的文件管理窗口看见

.v.out

的文件

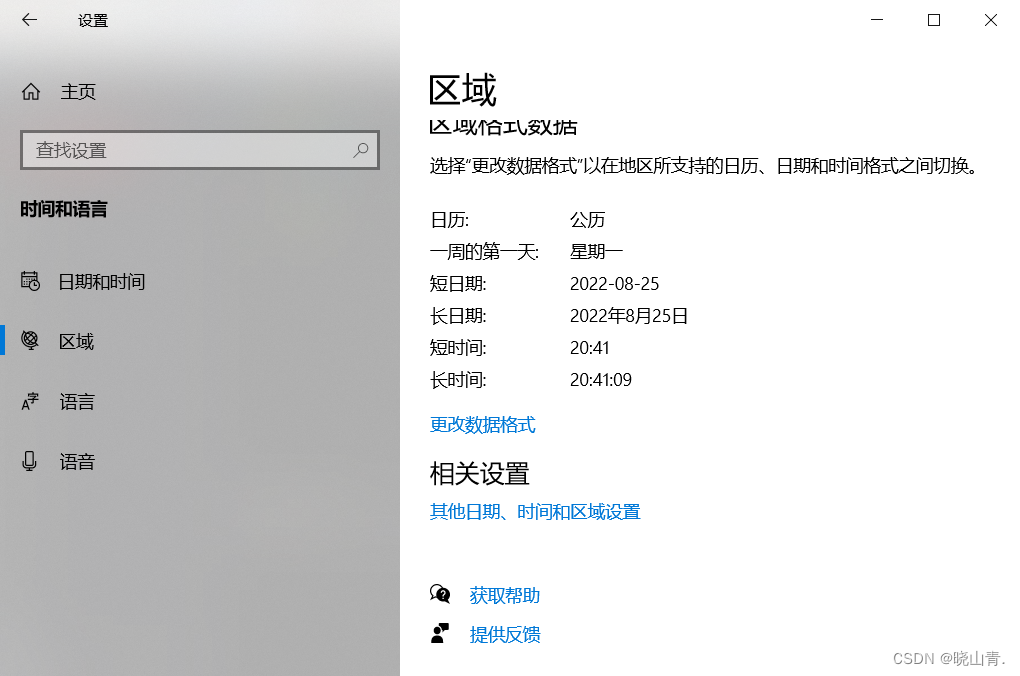

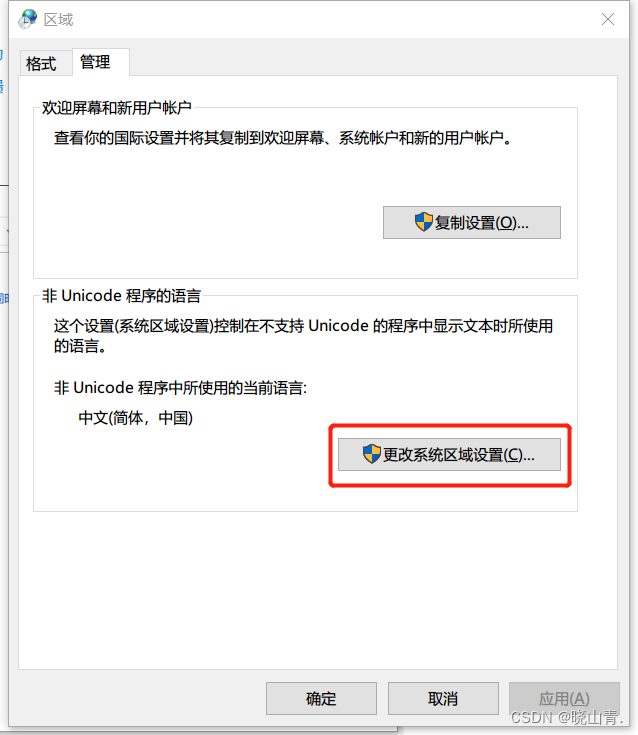

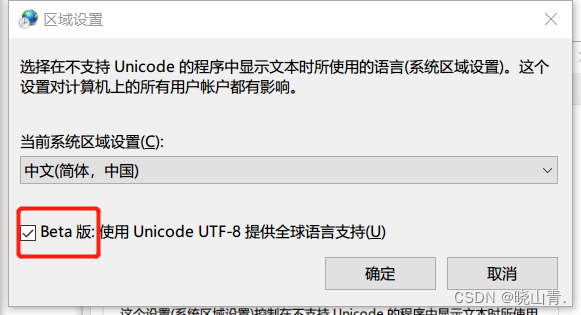

如果发现输出框出现的是一堆乱码,打开设置中的时间和语言-其他日期、时间和区域设置

点击区域

点击更改系统区域设置

勾选方框,点击确认即可

之后Vscode便能正常编译了

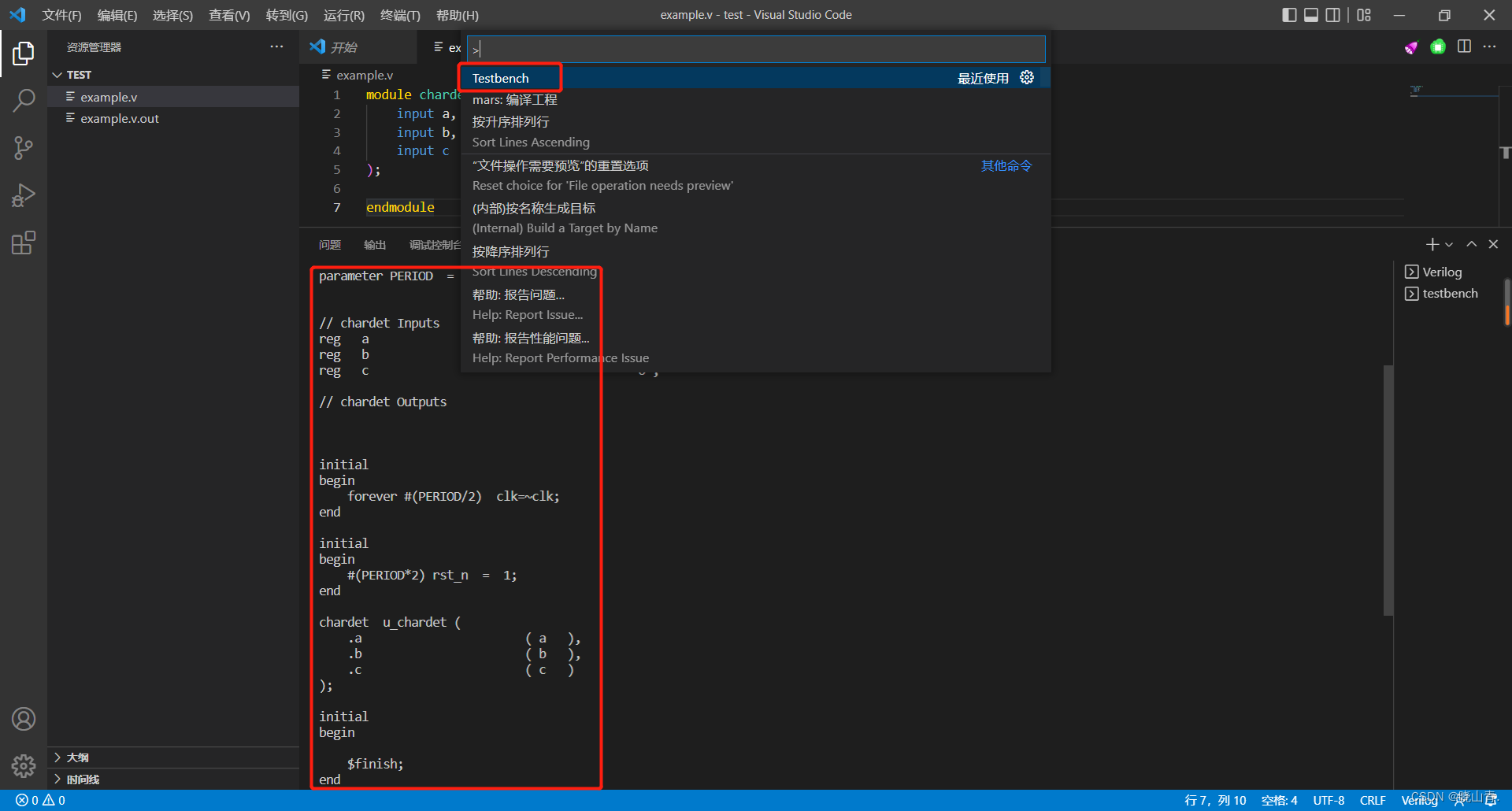

生成Testbench模板

在VScode使用快捷键

Ctrl+Shift+P

打开功能键,输入或者选择Testbench,运行,即可在终端中显示生成的模板文件,复制内容生成tb文件即可,但要注意的是**文件后缀仍然是

.v

**

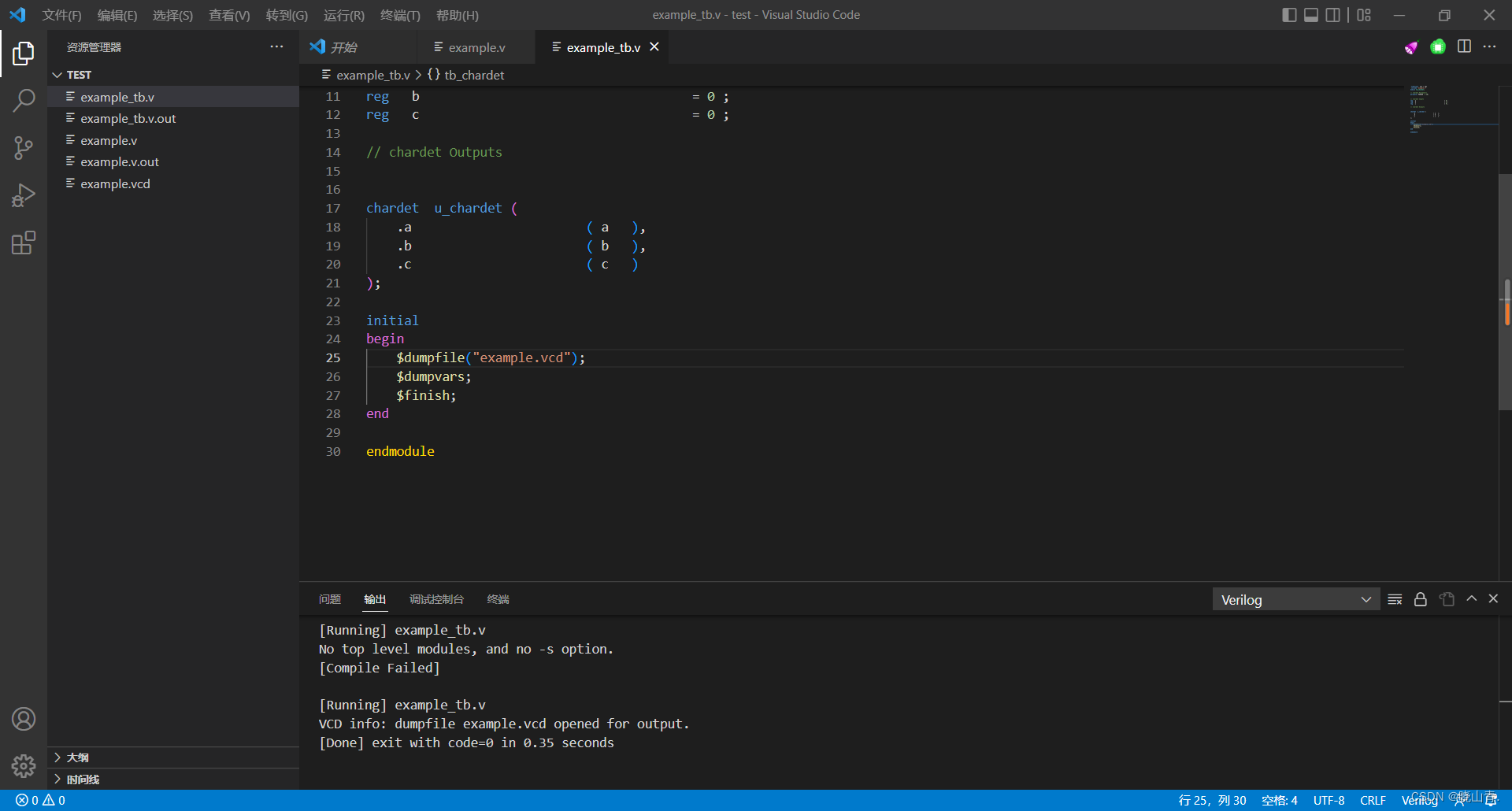

编写Testbench生成vcd文件

将终端中的内容复制到tb文件中,删除带PERIOD的两个initial模块,并且在第二行添加``include “主文件名.v”`,在这里是

`include "example.v"

接下来在initial中添加

$dumpfile("波形文件名.vcd");

$dumpvars;

其中

$dumpfile

指定波形文件名,

$dumpvars

表示所有定义的

wire

和

reg

都参与仿真。

再自行设置测试数据(在dumpvars和finish的中间添加状态代码)后点击运行,即可发现tb文件的

.v.out

文件,同时还有

vcd

文件。

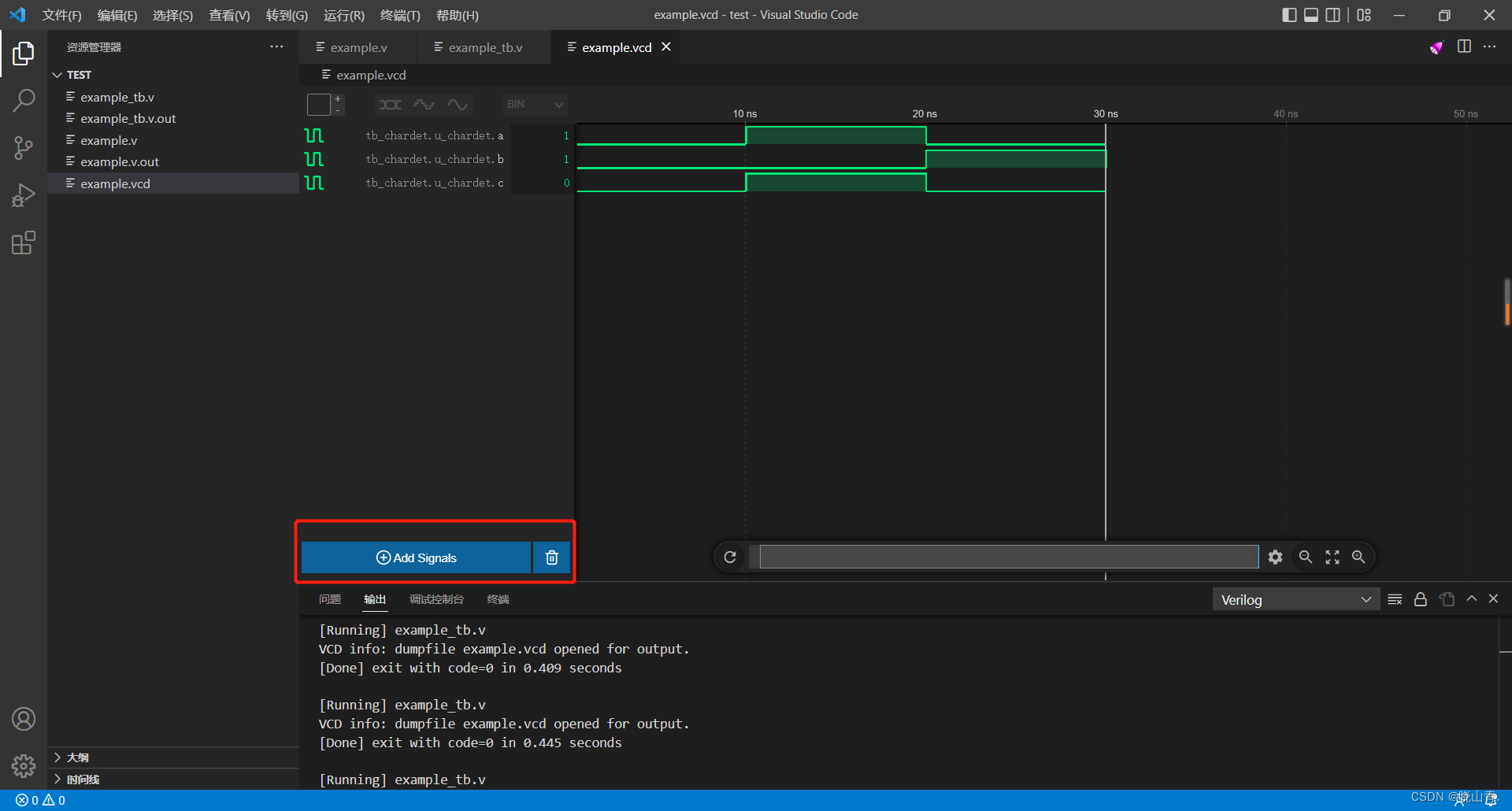

观察仿真波形

方法一:打开

vcd

文件,添加变量,即可实现波形的观察。

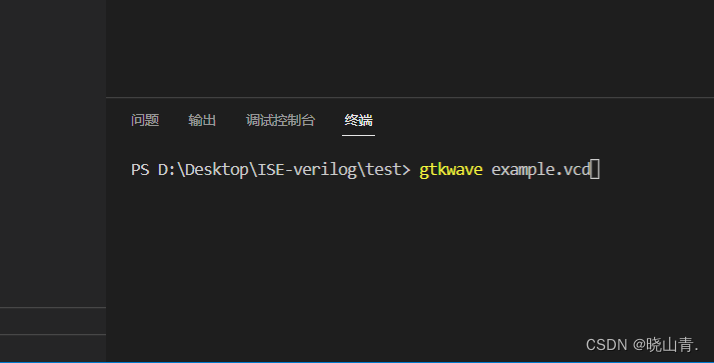

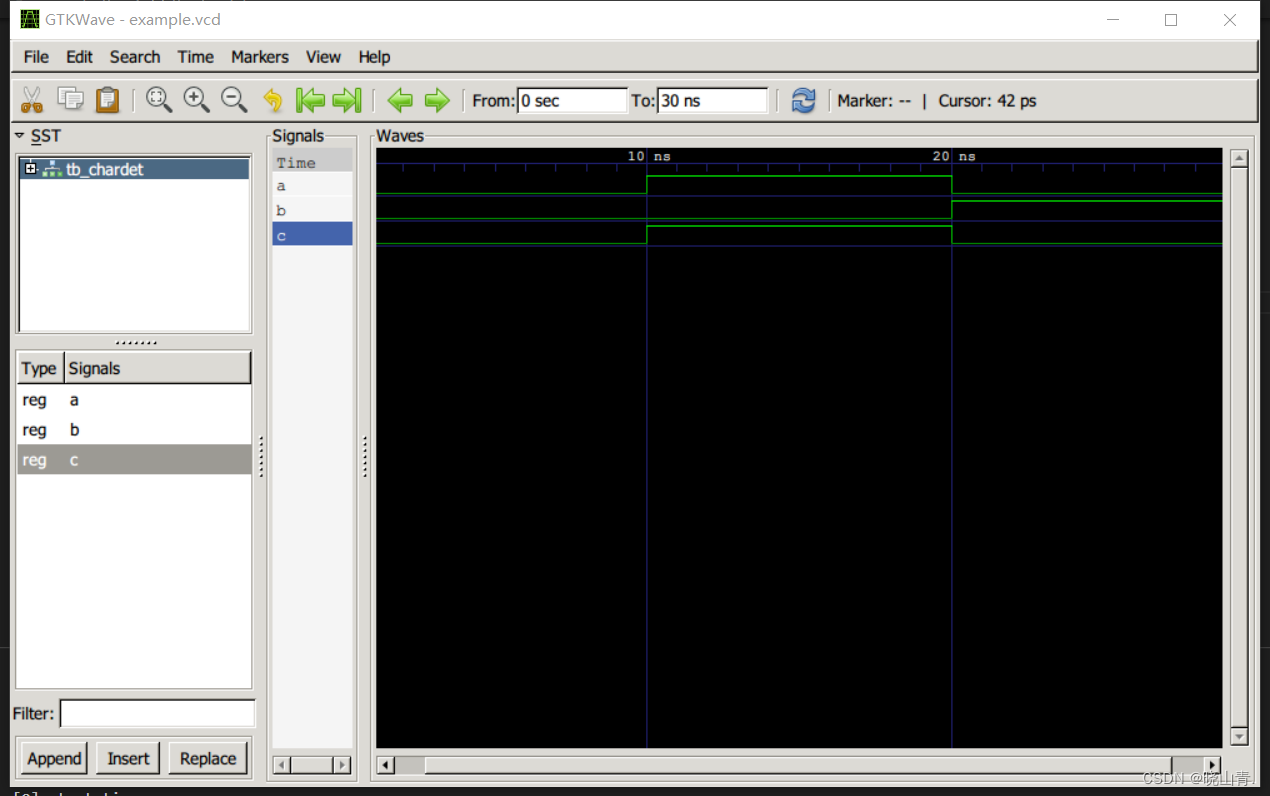

方法二:在终端中输入gtkwave XXX.vcd

之后便会打开gtkwave软件查看波形

至于其他的功能,那就请读者自行探索了~

版权归原作者 晓山青. 所有, 如有侵权,请联系我们删除。