2023年第一篇文章来咯~

8指令多周期(硬布线)MIPS CPU设计报告

一、设计概述(基本类似于上一篇)

1.1设计目的

- 本课程设计是完成该课程并进行了多个单元实验后,综合利用所学的理论知识,并结合在单元实验中所积累的计算机部件设计和调试方法,设计简单计算机系统。所设计的系统能在 LOGISIM 仿真平台上正确运行,通过检查程序结果的正确性来判断所设计计算机系统正确性。

- 本课程设计属于设计型实验,不仅锻炼学生简单计算机系统的设计能力,而且通过进行中央处理器底层电路的实现、故障分析与定位、系统调试等环节的综合锻炼,进一步提高学生分析和解决问题的能力。

1.2设计任务

本课程设计的总体目标是利用 LOGISIM 仿真平台,设计MIPS CPU,要求所设计的CPU 系统能支持自动和单步运行方式,能正确地执行存放在主存中的程序的功能,对主要的数据流和控制流通过 LED、数码管等适时的进行显示,方便监控和调试。利用仿真软件对模型机系统中各部件进行仿真分析和功能验证。具体设计任务如下:

在logisim平台利用已给出的组件构建一个32位MIPS多周期CPU,该CPU支持如表1. 1列出的核心指令集中的8条指令。要求绘制多周期MIPS CPU数据通路,实现硬布线控制器,并最终能在完成的CPU上运行冒泡排序的测试程序sort.hex且获得正确的输出结果。

表1.1 8条核心指令集

MIPS指令格式addr d , rd, rd,rs,$rtR[ r d ] ← R [ rd]←R[ rd]←R[rs]+R[ r t ] 溢出时产生异常,且不修改 R [ rt] 溢出时产生异常,且不修改R[ rt]溢出时产生异常,且不修改R[rd]slt r d , rd, rd,rs,$rtR[ r d ] ← R [ rd]←R[ rd]←R[rs]<R[$rt] 小于置1,有符号比较addi r t , rt, rt,rs,immR[ r t ] ← R [ rt]←R[ rt]←R[rs]+SignExt16b(imm) 溢出产生异常lw r t , i m m ( rt,imm( rt,imm(rs)R[ r t ] ← M e m 4 B ( R [ rt]←Mem4B(R[ rt]←Mem4B(R[rs]+SignExt16b(imm))sw r t , i m m ( rt,imm( rt,imm(rs)Mem4B(R[ r s ] + S i g n E x t 16 b ( i m m ) ) ← R [ rs]+SignExt16b(imm))←R[ rs]+SignExt16b(imm))←R[rt]beq r s , rs, rs,rt,immif(R[ r s ] = R [ rs] = R[ rs]=R[rt]) PC ← PC + SignExt18b({imm, 00})bne r s , rs, rs,rt,immif(R[ r s ] ! = R [ rs] != R[ rs]!=R[rt]) PC ← PC + SignExt18b({imm, 00})syscall系统调用,这里用于停机

1.3设计要求

(1)根据课程设计指导书的要求,制定出设计方案;

(2)分析指令系统格式,指令系统功能;

(3)根据指令系统构建基本功能部件,主要数据通路;

表 1.2 24条核心指令集

指令格式Addadd $rd, $rs, $rtAdd Immediateaddi $rt, $rs, immediateAdd Immediate Unsignedaddiu $rt, $rs, immediateAdd Unsignedaddu $rd, $rs, $rtAndand $rd, $rs, $rtAnd Immediateandi $rt, $rs, immediateShift Right Arithmeticsra $rd, $rt, shamtShift Right Logicalsrl $rd, $rt, shamtSubsub $rd, $rs, $rtOror $rd, $rs, $rtOr Immediateori $rt, $rs, immediateNornor $rd, $rs, $rtLoad Wordlwr t , o f f s e t ( rt, offset( rt,offset(rs)Store Wordsw r t , o f f s e t ( rt, offset( rt,offset(rs)Branch on Equalbeq $rs, $rt, labelBranch on Not Equalbne $rs, $rt, labelSet Less Thanslt $rd, $rs, $rt备注:指令功能及指令格式参考 MIPS32 指令集

指令格式Set Less Than Immediateslti $rt, $rs, immediateSet Less Than Unsignedsltu $rd, $rs, $rtJumpj labelJump and Linkjal labelJump Registerjr $rs备注:指令功能及指令格式参考 MIPS32 指令集

指令格式syscall(display or exit)Syscall备注:If v 0 = = 34 数码管显示 v0==34 数码管显示 v0==34数码管显示a0值 else halt(停机指令) (4)根据功能部件及数据通路连接,分析所需要的控制信号以及这些控制信号的有效形式; (5)设计出实现指令功能的硬布线控制器和微程序控制器; (6)调试、数据分析、验收检查; (7)课程设计报告和总结。

1.4技术指标

(1)支持表 1.1 中8 条基本 32 位 MIPS 指令;

(2)能运行由自己所设计的指令系统构成的一段测试程序,测试程序应能涵盖;

(3)所有指令,程序执行功能正确;

(4)能运行教师提供的标准测试程序,并自动统计执行周期数。

二、总体方案设计

2.1主要功能部件

- 1、指令计数器:在时钟沿到来时,用NPC的值更新PC。

- 2、指令存储器:将PC输入的地址对应的指令输出。

- 3、指令寄存器:在时钟沿到来时,用从IM取出的指令更新。

- 4、寄存器组:本系统的寄存器组,可以读出指令中指定rs,rt对应的寄存器的数据,也能在时钟沿到来时将WDSel指定数据源的数据写入WRSel指定的寄存器之一。

- 5、扩展单元:将输入的16位立即数按照EXTOp信号进行零扩展或符号扩展(注:在设计的其他地方也同样使用到了扩展单元,且扩展的位数和方式各有不同。

- 6、数据寄存器:在时钟沿到来时,将从RF中取出的数据保存。

- 7、扩展寄存器:在时钟沿到来时,将EXT扩展得到的数据保存。

- 8、ALU输入:按照BSel,从RFRD2,E中选择一个作为B的输入;按照CSel,从IMM和常数d16选择一个作为C的输入。最终,操作数A,B,C扩展后将作为ALU输入。

- 9、ALU(数逻运算单元):将A,B,C输入的操作数按照ALUOp信号进行相应的算术运算、逻辑运算或移位操作,输出为D。

- 10、信号生成部件:利用“按位与”,以及输出D的符号位生成返回信号zero和sign。

- 11、ALUOUT(执行部件输出寄存器):将按照ALUOp,利用输出D和返回信号sign,zero得到最终的输出值,在时钟沿到来时进行更新。

- 12、数据存储器:按照ALUOUT给出的地址,将从RF读出的数据在时钟沿到来时写入存储器;或从存储器中读出对应地址的数据。

- 13、数据寄存器:在时钟沿到来时,将从RAM中读出的数据写入DR。

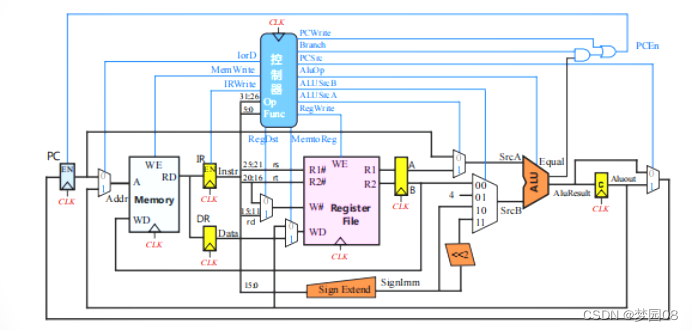

2.2数据通路设计

- 多周期 CPU 指的是将整个 CPU 的执行过程分成几个阶段,每个阶段用一个时钟去完成,然后开始下一条指令的执行,而每种指令执行时所用的时钟数不尽相同,这就是所谓的多周期 CPU。CPU 在处理指令时,一般需要经过以下5个阶段:

- 1.取指令:根据程序计数器 pc 中的指令地址,从存储器中取出一条指令,同时, pc 根据指令字长度自动递增产生下一条指令所需要的指令地址,但遇到“地址转移”指令时,则控制器把“转移地址”送入 pc,当然得到的“地址”需要做些变换才送入 pc。

- 2.指令译码:对取指令操作中得到的指令进行分析并译码,确定这条指令需要完成的操作,从而产生相应的操作控制信号,用于驱动执行状态中的各种操作。

- 3.指令执行:根据指令译码得到的操作控制信号,具体地执行指令动作,然后转移到结果写回状态。

- 4.存储器访问:所有需要访问存储器的操作都将在这个步骤中执行,该步骤给出存储器的数据地址,把数据写入到存储器中数据地址所指定的存储单元或者从存储器中得到数据地址单元中的数据。

- 5.结果写回:指令执行的结果或者访问存储器中得到的数据写回相应的目的寄存器中。

- 构建多周期MIPS CPU数据通路:

- 硬布线控制器的设计:和单周期CPU相比,只是讲微指令控制器改变成硬布线控制器,而其他部分开没有发生改变,数据通路部分和微指令控制器多周期MIPS CPU一样,原理也相同。

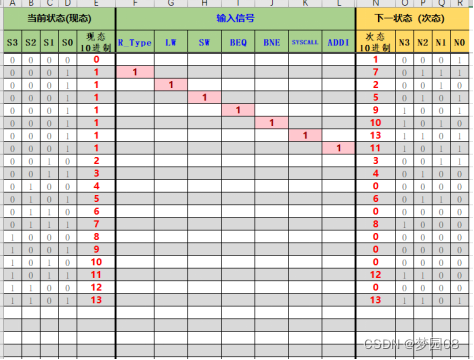

- 多周期硬布线除控制状态机外都相同,这次多周期硬布线的主要任务就是设计状态机,设计方法如下:根据状态转换图填写Excel

- 生成状态机:

- 最后测试结果即可。

三、详细设计与实现

3.1主要功能部件的实现

- 1.指令计数器/指令存储器:通过PCSrc控制是跳跃寻址还是顺序寻址。在储器中读取指令,并交给IR和DR两个寄存器暂存。

- 2.寄存器组:根据输入的地址,存入需要存储的数据并在下一个时钟周期输出。

- 3.扩展单元:将16位立即数进行零扩展或者符号扩展。

- 4.ALU:根据计算选择器ALUSrcA、B来判断输入并根据ALUOP来判断进行什么计算,根据PCSrc判断是否跳跃寻址。

- 5.多周期硬布线控制器:根据输入的PC和Func来控制电路的整体工作状态。

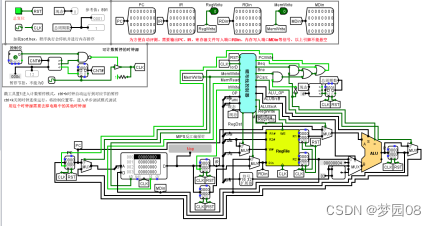

3.2数据通路的实现

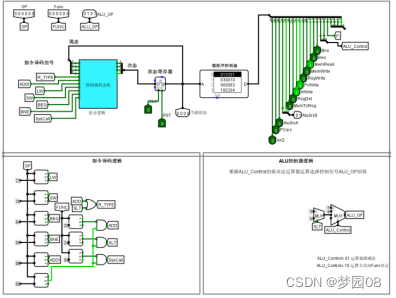

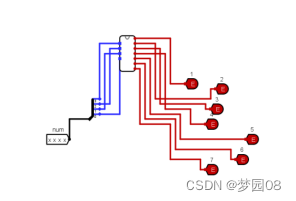

- 多周期MIPS CPU数据通路(美化后)如下图:

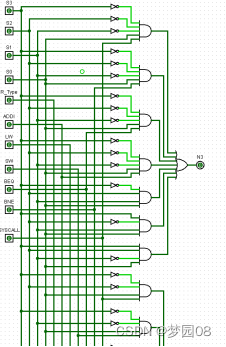

3.3硬布线控制线的实现

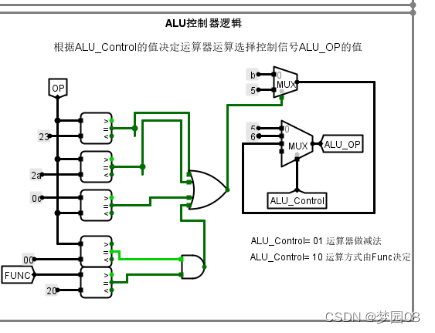

- 指令译码逻辑与单周期类似,但是ALU控制ALUControl控制ALUControl受当前状态影响依据不同状态有不同的值。

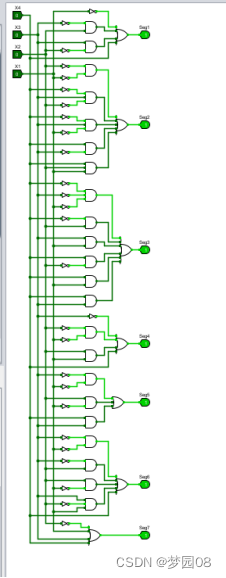

- 硬布线控制器线路如下图:

四、实验过程与调试

4.1硬布线故障及分析

- 故障现象:

- 原因分析:ALU控制器出现错误导致将错误的地址返回PC,PC通过错误的地址得到的错误的结果输出

- 解决方案:改正ALU控制器端口

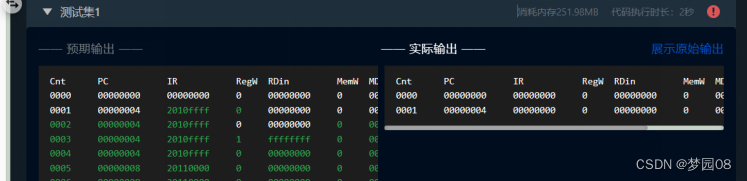

4.2测试用例和功能测试

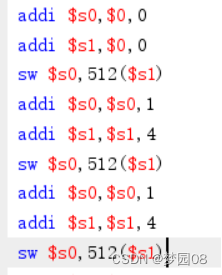

4.2.1 数据读入(addi指令,sw指令)

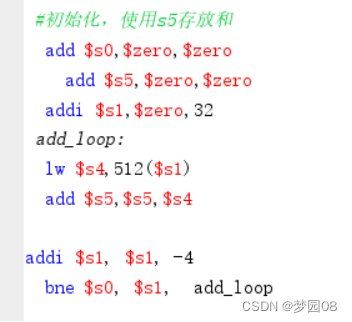

4.2.2 数据求和(add指令,bne指令)

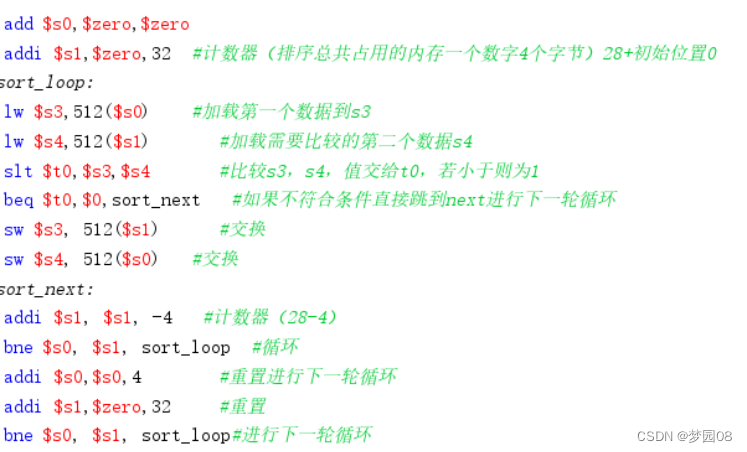

4.2.3 数据排序(简单的选择排序(正序和倒序),beq)

- 数据排序

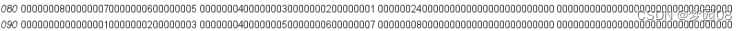

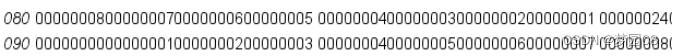

- 结果如图,倒序排序,求和,正序排序:

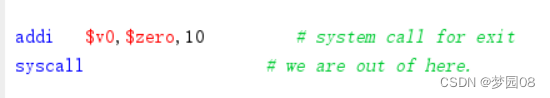

4.2.4 结束指令(v0=10,syscall)

4.2.5 数据的展示

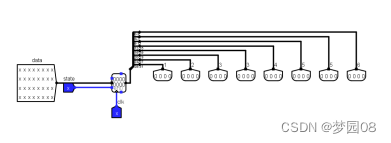

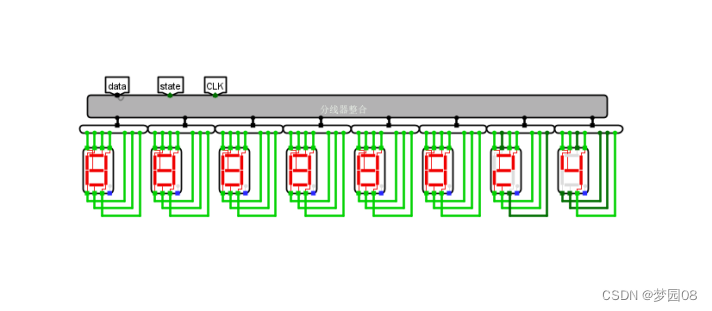

- 设计数码管驱动,并封装设计出能输出所求数据和的电子数码管。

- 数据展示如下:

- 线路如下:

- 封装好后的电路,传入data(写入存储器的数字),和state(MemWrite),在程序结束后输出最后一个存入的数据。(当然,要提前写好汇编指令,让其最后一个存入的是所求的和)

- 实现原理:和数据存储器类似,将每次的数据写入寄存器中,保存起来并输出。

- 数据展示如下图:

结果如图所示:

结果如图所示:

五、设计总结与心得

- 在独立实现 CPU 设计的过程中,我不断地重温理论课的知识,并以此指导实践过程,我想这不仅是对我理论知识的考验,也是对我工程能力、实践能力的锻炼,更是对我心智的磨砺与充实。在花费了一周的时间深入学习,并花费近一周的时间中数十个小时的努力之后,我终于在实现了单周期、多周期的处理器,并经过调试工作最终通过了仿真测试。

- 本设计在实现过程中尽可能地尝试降低对硬件资源的使用情况,同时尽可能地简化设计。在这两点的基础上,设计整体呈现出了比较好的性能,在与同学交流的过程中,也获悉本设计的硬件资源使用情况、功耗情况相对较低,最大系统时钟频率相对较高。总的来说,该设计性能比较优秀。另一方面,在性能分析的过程中可以注意到,随着系统时钟频率的增加,系统的功耗有所提高。

六、参考文献

[1] 袁春风,武港山,吴海军,余子濠.数字逻辑与计算机组成 [M].北京:机械工业出版社,2021.

[2] 谭志虎,秦磊华,吴非,肖亮.计算机组成原理[M].北京:人民邮电出版社,2021.

[3] 谭志虎,周军龙,肖亮.计算机组成原理实验指导与习题解析. [M].北京:人民邮电出版社,2022.

[4] DAVID A.PATTERSON(美).计算机组成与设计硬件/软件接口(原书第5版).北京:机械工业出版社.

[5] David Money Harris(美).数字设计和计算机体系结构(第二版).机械工业出版社.

[6] 谭志虎,秦磊华,胡迪青.计算机组成原理实践教程.北京:清华大学出版社,2018年.

[7] 秦磊华,吴非,莫正坤.计算机组成原理. 北京:清华大学出版社,2011年.

[8] 袁春风编著. 计算机组成与系统结构. 北京:清华大学出版社,2011年.

[9] 张晨曦,王志英. 计算机系统结构. 高等教育出版社,2008年.

结束语

希望这篇文章会对大家有帮助,也希望大家在编程的道路上越走越远,早日成为IT届大佬!!!

后续将持续更新,大家的支持就是我创作的动力!!!

版权归原作者 小园园子 所有, 如有侵权,请联系我们删除。