🔥 本文由 程序喵正在路上 原创,CSDN首发!

💖 系列专栏:虚拟机

🌠 首发时间:2022年9月10日

🦋 欢迎关注🖱点赞👍收藏🌟留言🐾

🌟 一以贯之的努力 不得懈怠的人生

阅读指南

什么是gcc?

- Linux 环境下编译 C 语言程序的工具

在命令终端输入:

gcc -v

可以查询当前系统安装的 gcc 版本

如果我们有 hello.c 的 C 语言源代码,那么编译的命令是:

gcc -o hello hello.c

gcc处理源代码的流程

- 预处理阶段:对 .c 文件的包含、预处理等语句的处理,并生成名为 test.i 的中间文件

- 编译阶段:以 test.i 为输入,编译生成汇编语言文件 test.s

- 汇编阶段:以 test.s 为输入,生成目标文件 test.o

- 链接阶段:将使用到库函数链接到可执行程序中的正确位置,形成二进制代码文件

gcc常用的参数选项

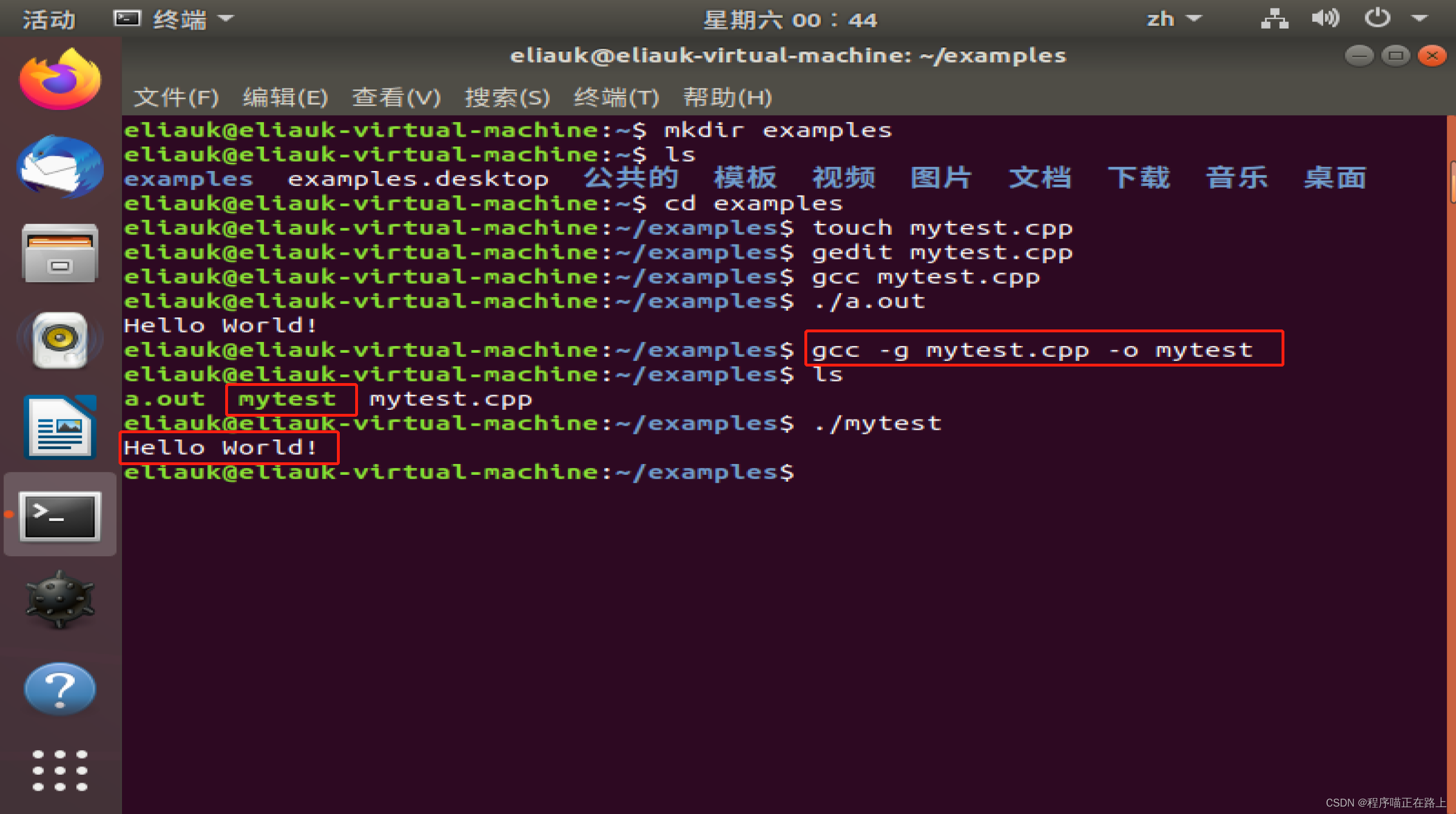

-c:仅生成拓展名为 .o 的目标文件,不链接生成可执行文件-o 文件名:指定 gcc 可执行文件名,系统默认生成的可执行文件名为 a.out-g:编译时加入调试信息,使得后期方便对程序进行调试,主要是为支持 gdb 的调试

Ubuntu下的C程序

那么在 ubuntu 中我们怎么来创建和编辑 C 语言程序呢?

很简单

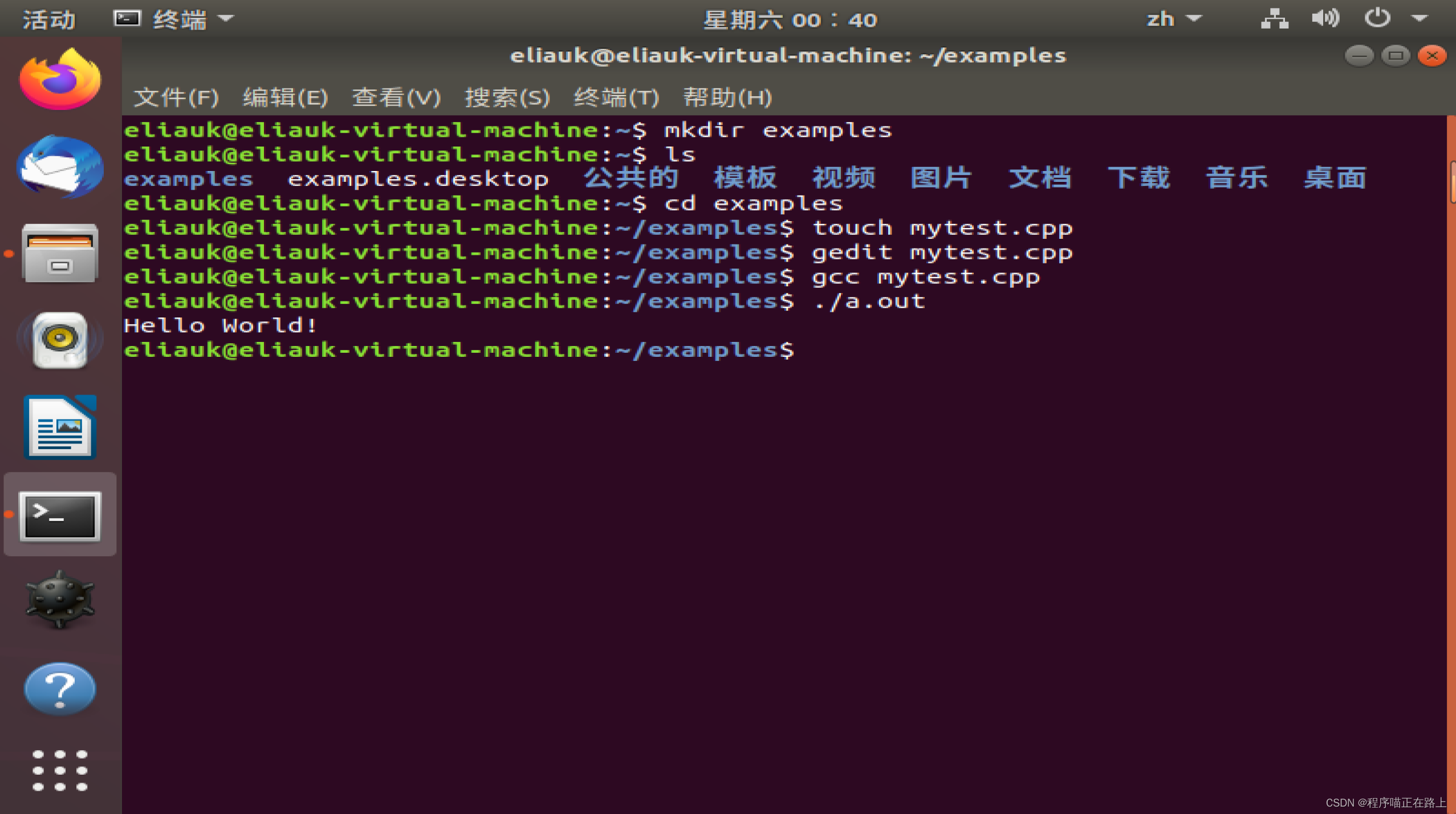

- 使用 Ctrl + Alt + t 打开终端

- 使用

mkdir 文件夹名来创建文件夹 - 使用

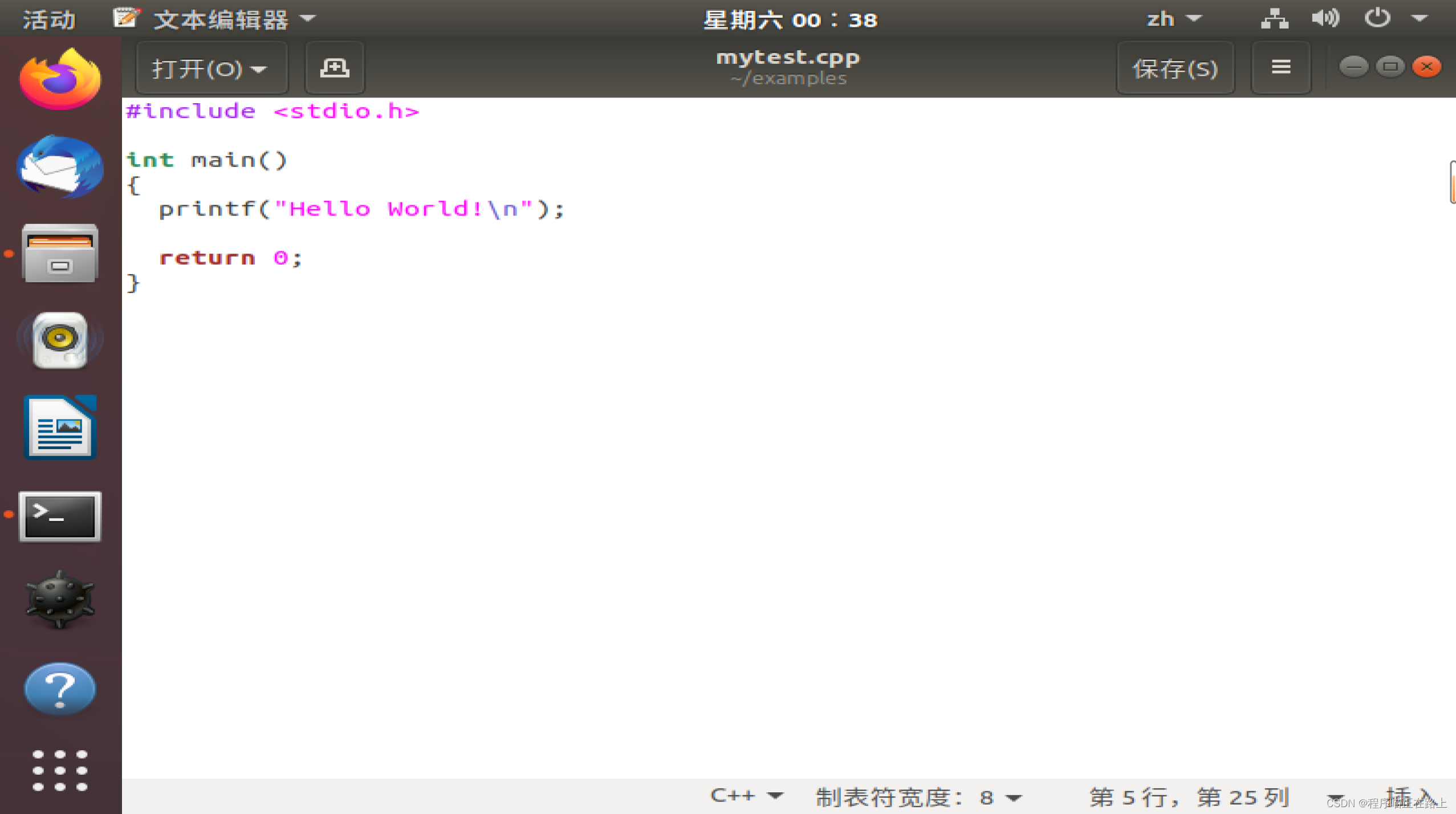

touch mytest.cpp创建 C 文件 - 创建完 C 文件后,我们需要进行编写文件。ubuntu 中提供了一个程序编辑软件 gedit,我们借助命令

gedit mytest.cpp就会弹出编辑对话框,如何就可以在其中进行编辑,当然你也可以选择找到 mytest.cpp 后双击打开 - 编辑完记得保存文件

- 在命令行中输入

gcc mytest.cpp编译文件,若没有出错则编译成功 - 编译成功后会生成一个可执行文件 a.out,在命令行中输入

./a.out运行程序

mytest.cpp

操作如图:

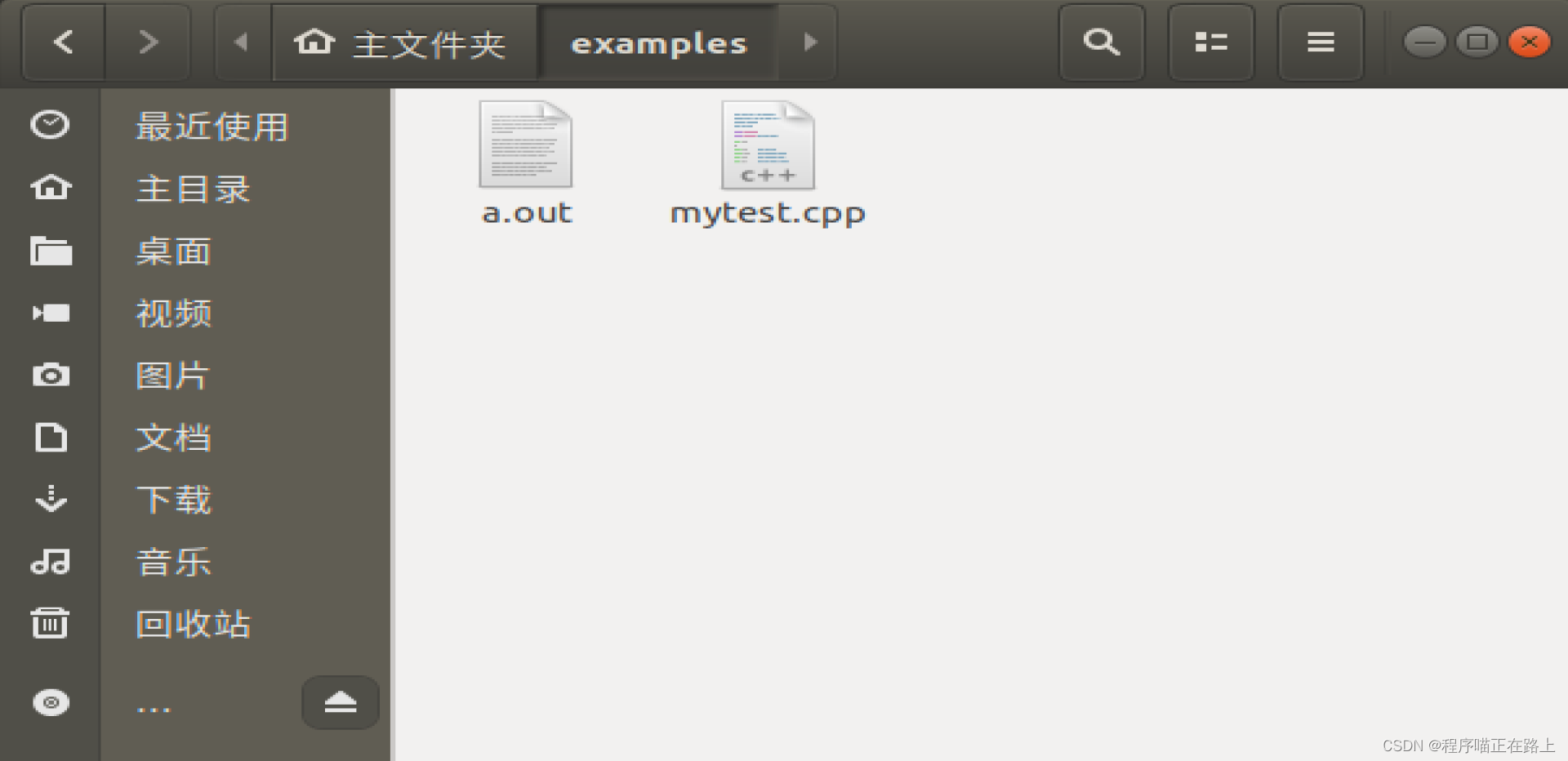

编译后可以发现多了一个 a.out 文件

刚才的编译是没有带参数的,下面我们试试看使用带参数的编译

gdb的简单使用

什么是 gdb ?

- gdb 是 gnu 开源组织发布的、用来调试 C 程序的调试工具

怎么使用?

gdb 程序名

常用的 gdb 功能如下

list 命令:显示程序源代码break 行号:给程序对应的行号打断点break 函数名:给函数的入口设置断点info break:查看全部断点信息delete 断点号:删除对应编号的断点run:开始运行程序,直到遇到断点continue(缩写为 c):程序继续执行next(缩写为 n):执行下一语句quit:退出调试

直接采用gcc编译文件的问题

当一个应用程序涉及到的 C 语言源代码文件达到成百上千后,直接采用 gcc 编译会出现以下问题:

- 手动去敲每个编译命令不现实

- 当修改某个文件时,要避免对所有的文件进行编译链接,只对依赖该文件的部分进行重新编译链接,节省时间

Makefile

什么是Makefile?

- 自动化编译 C 语言程序的脚本工具

为什么需要 Makefile 呢?

- 为了解决 gcc 编译的不足

如何使用 Makefile?

- 根据应用程序的文件数量,依赖关系等书写 Makefile 编译脚本

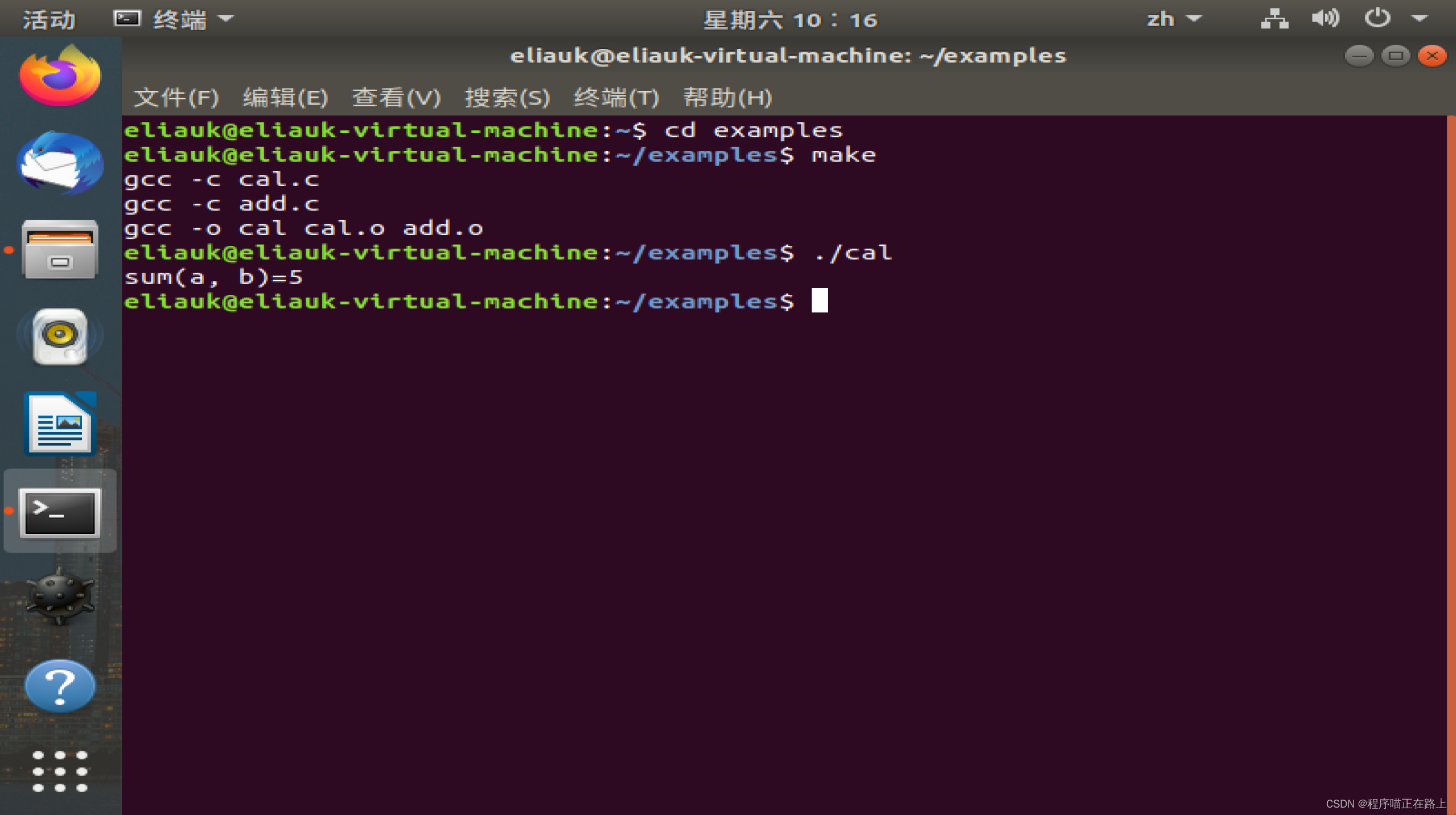

- 包含 Makefile 编译脚本的目录下,敲击 make 命令

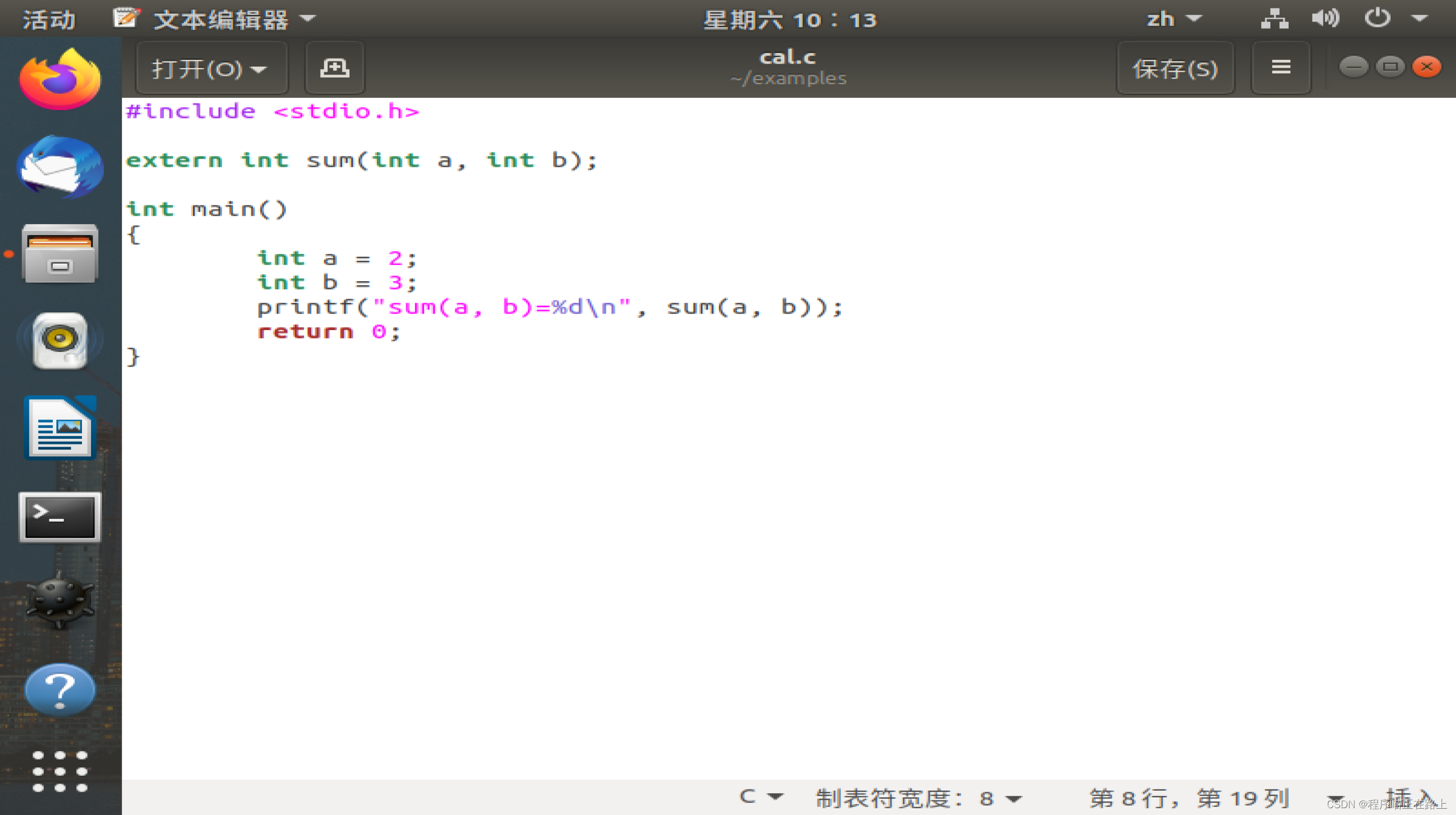

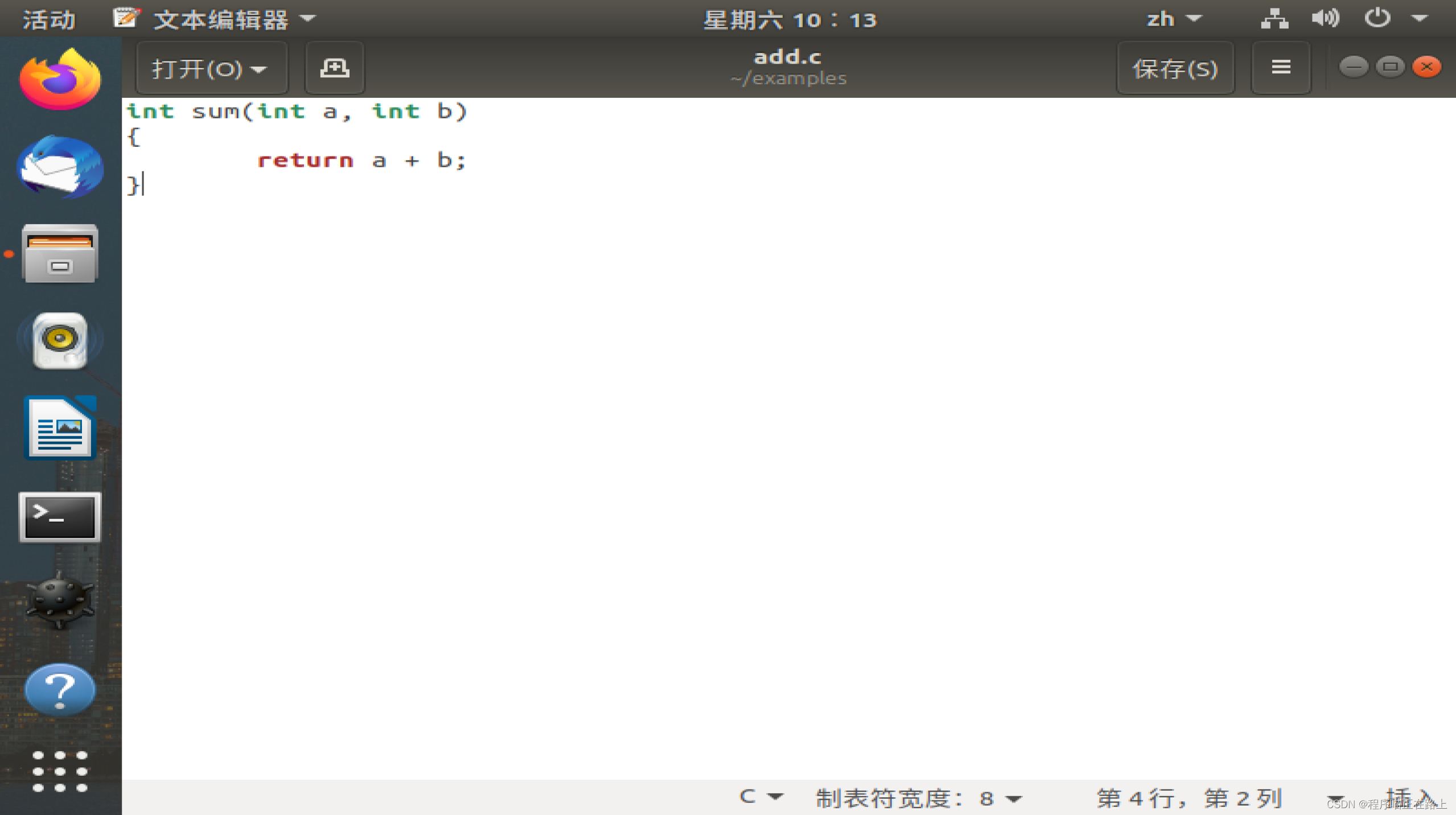

创建两个文件:cal.c 和 add.c

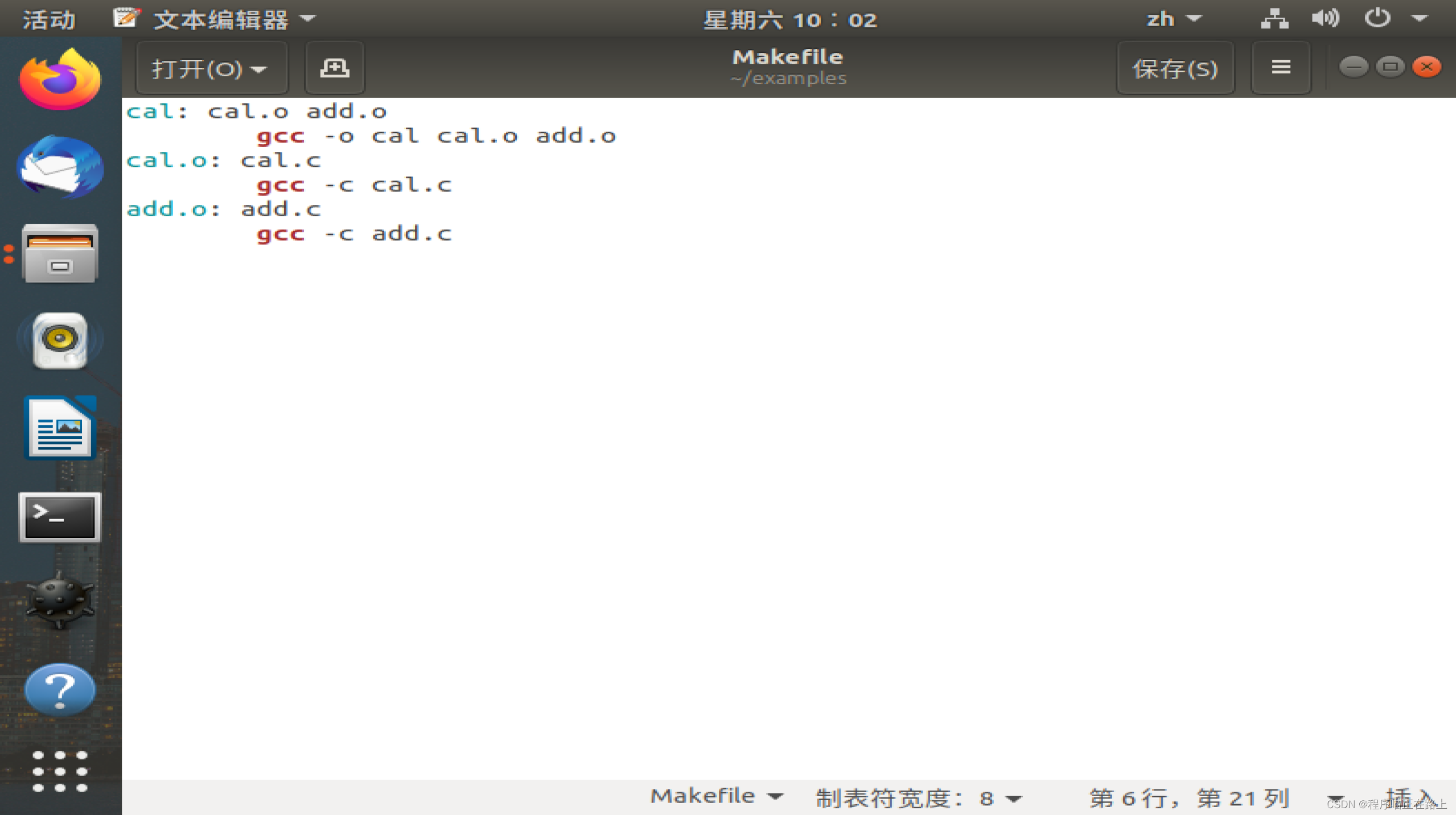

对应的 Makefile:

cal: cal.o add.o

gcc -o cal cal.o add.o

cal.o: cal.c

gcc -c cal.c

add.o: add.c

gcc -c add.c

冒号左边的文件依赖于右边的文件

在 cal.c 和 add.c 文件的同目录下创建一个名为 Makefile 的文本文件:

Makefile 的自动推导功能

make 命令可以自动推导文件以及文件依赖关系后面的命令,make 会自动识别并自己推导命令。只要 make 查到某个 .o 文件,它就会自动把相关的 .c 加到依赖文件中

Makefile 常用的符号

- **$@**:表示当前目标文件的名字

- $^:表示用空格隔开的所有依赖文件

- **$<**:表示第一个依赖文件

- **$+**:与 $^ 类似,只是没有排除重复的条件

- **$***:目标的主文件名,不包含拓展名

简化的 Makefile 如下:

cal: cal.o add.o

gcc -o $@ $^

cal.o: cal.c

gcc -c $<

add.o: add.c

gcc -c $<

多层次目录结构的Makefile

之前的案例:cal.c、add.c 源代码与 Makefile 在同一个目录

现在:cal.c 和 add.c 位于 src 目录,而 Makefile 位于 src 的父级目录

要求:编译 cal.c 和 add.c 文件,并将可执行文件放置于父级目录

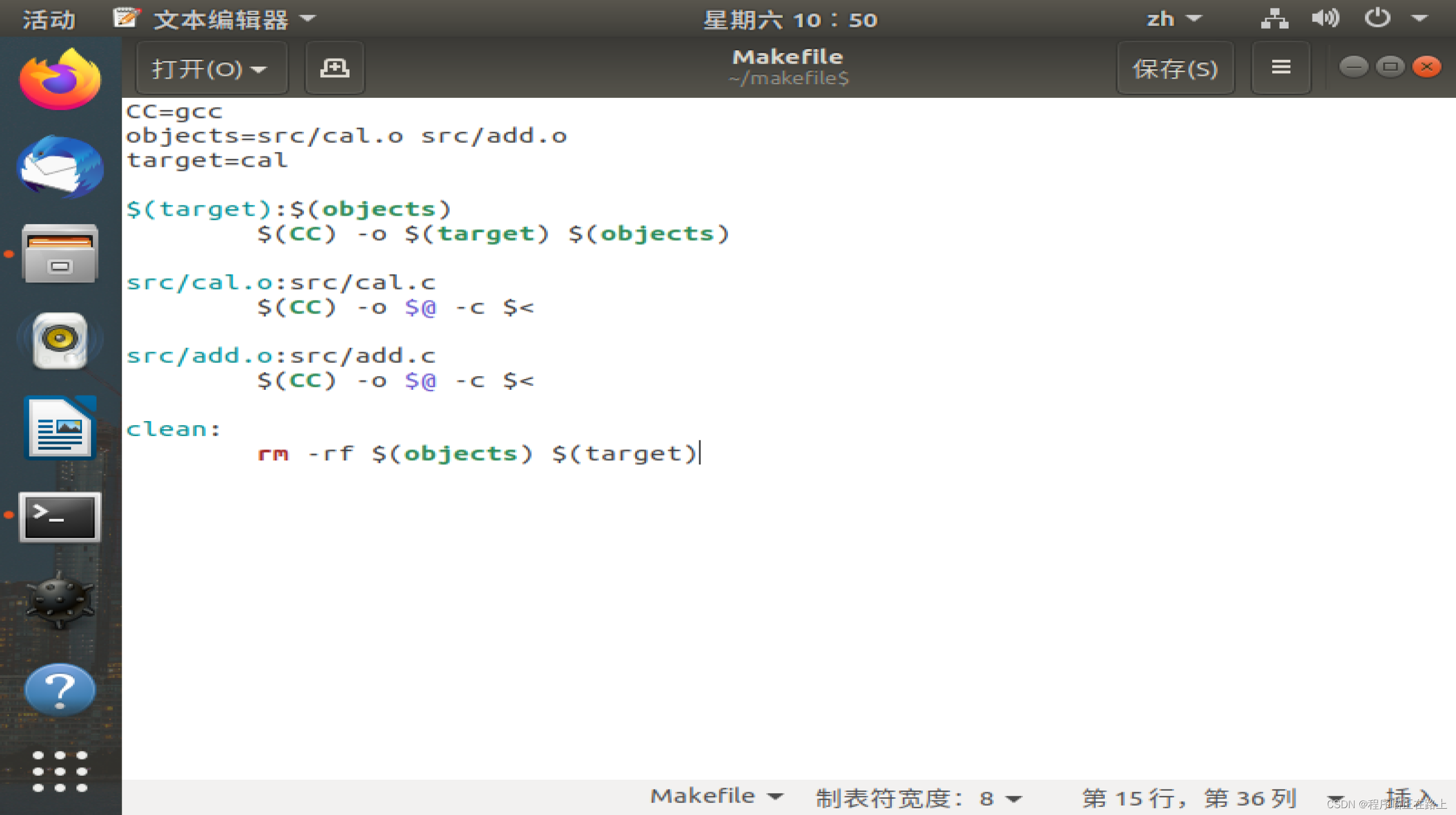

环境需要自己准备,记得将 Makefile 改成这样:

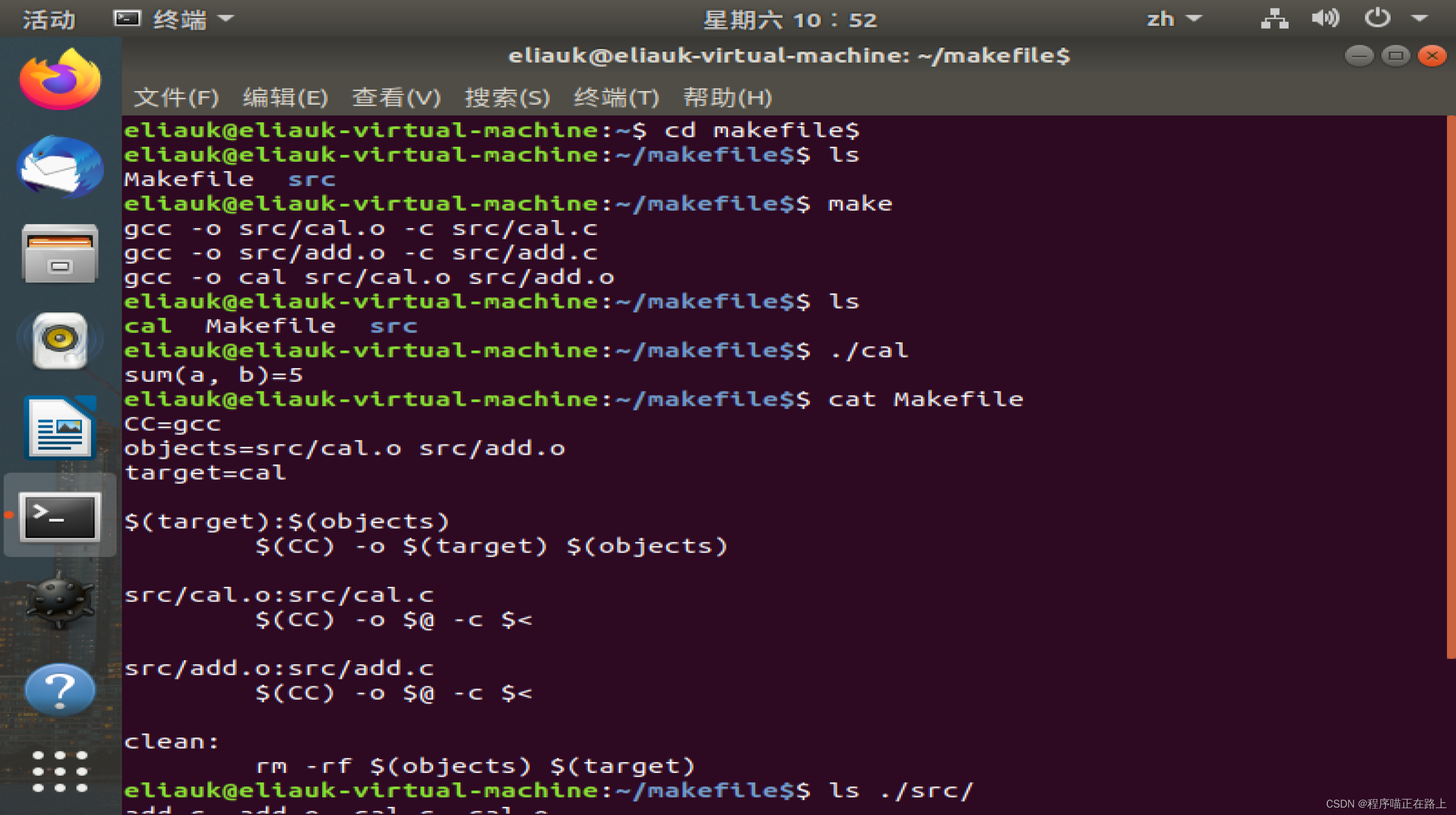

编译运行过程:

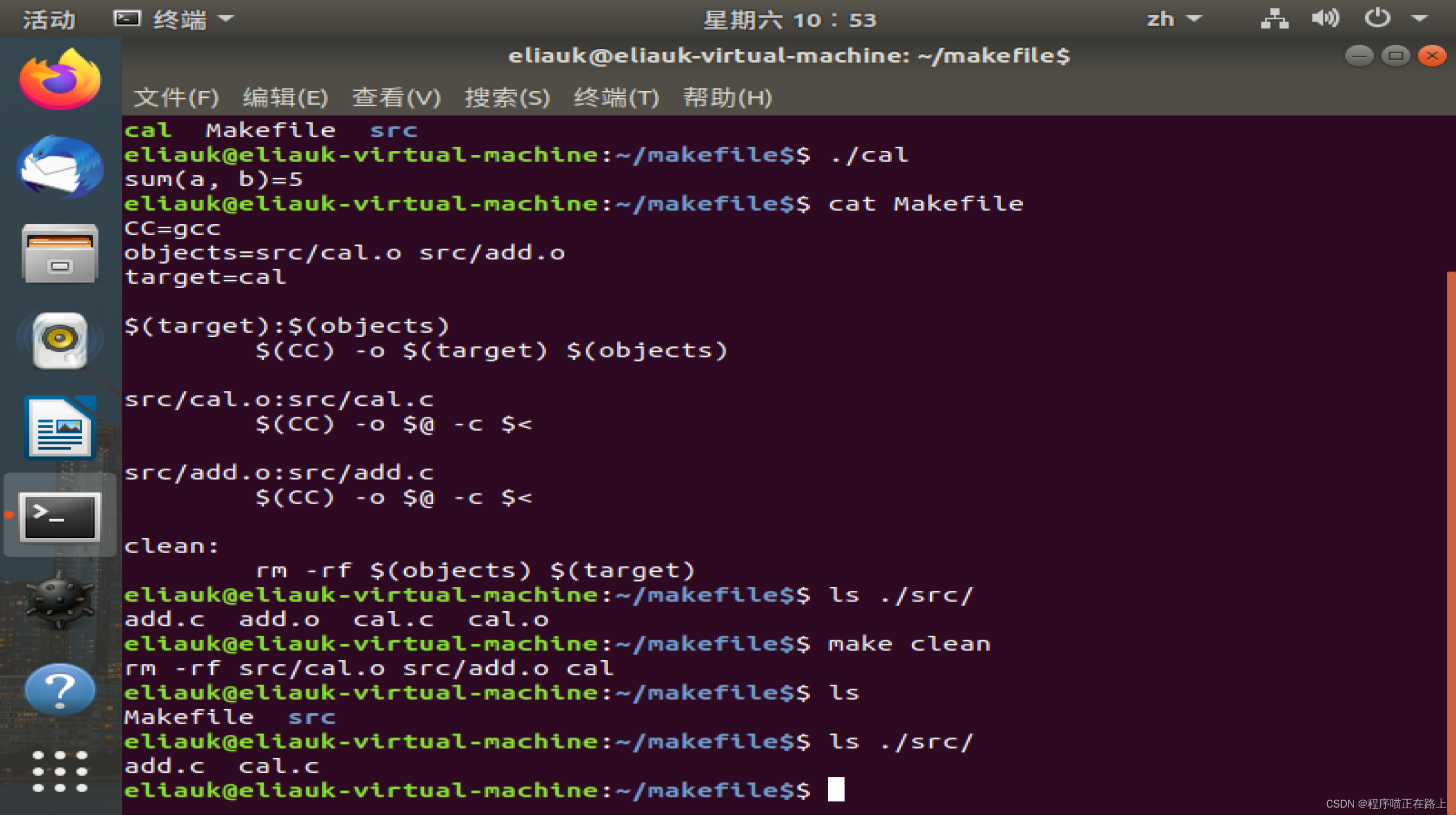

清理掉不需要的文件:

版权归原作者 程序喵正在路上 所有, 如有侵权,请联系我们删除。