4.用VHDL语言设计一个4位先行进位加法器

① 理解要求,需要完成一个先行进位加法器,可采取化简后的公式,直接用逻辑门构造一个4位先行进位加法器。

② 公式和原理图:

③ 打开QuartusII,新建工程,工程命名为adder_first,开始编写源代码。

④ 写好源代码,保存文件。

LIBRARY IEEE;

use IEEE.std_logic_1164.all;

entity adder_first is

port(a:in std_logic_vector(3 downto 0);

b:in std_logic_vector(3 downto 0);

cin:in std_logic;

s:out std_logic_vector(3 downto 0);

cout:out std_logic);

end adder_first;

architecture shixian of adder_first is

signal c:std_logic_vector(3 downto 0);

signal p:std_logic_vector(3 downto 0);

signal g:std_logic_vector(3 downto 0);

begin

p(0)<=a(0)xorb(0);p(1)<=a(1)xorb(1);p(2)<=a(2)xorb(2);p(3)<=a(3)xorb(3);g(0)<=a(0)andb(0);g(1)<=a(1)andb(1);g(2)<=a(2)andb(2);g(3)<=a(3)andb(3);c(0)<=g(0)or(cin andp(0));c(1)<=g(1)or(g(0)andp(1))or(cin andp(1)andp(0));c(2)<=g(2)or(g(1)andp(2))or(g(0)andp(2)andp(1))or(cin andp(2)andp(1)andp(0));c(3)<=g(3)or(g(2)andp(3))or(g(1)andp(3)andp(2))or(g(0)andp(3)andp(2)andp(1))or(cin andp(3)andp(2)andp(1)andp(0));s(0)<=p(0)xor cin;s(1)<=p(1)xorc(0);s(2)<=p(2)xorc(1);s(3)<=p(3)xorc(2);

cout<=c(3);

end shixian;

(如图为源代码)

⑤ 编译与调试。确保顶层实现的命名和工程名一致。编译成功。

⑥ 查看RTL视图。

⑦ 结果分析及结论。

如RTL图所示,该4位先行进位加法器图像满足之前所列的公式。

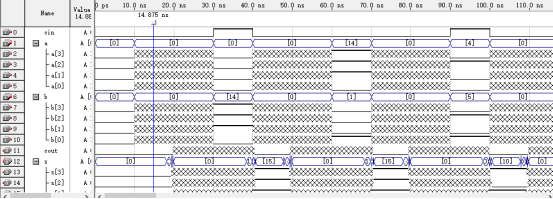

⑧ 功能仿真的波形及验证。

a.新建波形文件,将对应的16种输入存储在波形文件adder_first.vwf中。

b.生成网表。

c.进行功能仿真。

波形图如下图:

d.结果分析及结论

⑩ 实现时序仿真。

a.仿真成功。

b.时序仿真波形图如下:

c.结果分析及结论(为方便说明以及观测,A,B,S向量表示的二进制数用在分析过程中统一用十进制数表示)

d.编译【classic timing analysis】-在compilation report中选择【timing analysis】-【tpd】(引脚到引脚的延时)

从a0到s2耗时最长,为10.630ns,从c0到s0耗时最短,为7.705ns,可结果由耗时最长的那个决定,故整体耗时为10.630ns。

五、实验结论

1、思考题

① 多路复用器的实现方式很多,请总结两种以上实现方法。

答 :

1)通过采用多个较小的复用器,合成一个较大的多路复用器,如用2-1多路复用器经过组合实现一个更大的复用器

2)设计一个n为的多路复用器,再进行调用即可

② 总结 VHDL 语言描述多路复用器的方法的常用语句。

答:process statement 、component statement 、generate statement 、Function statement

2、实验总结与实验心得

答:

实验总结:本次实验实现了多路复用器的实现,同时进一步学习和了解了行波加法器和先行进位加法器的区别和相同之处,以及关于Quartus里程序包要如何进行设计和调用。其中一个要注意的地方就是,调用程序包或者在全加器中使用先行设计好的加法器时,要先通过component语句进行申明。

心得:本次实验进一步熟悉了Quartus的使用,最大的收获是学会了程序包的自我设计和调用。个人感觉这个和C++里在主函数外先设计一个外调函数,再在主函数中进行申明和(赋值)调用十分相像。

版权归原作者 灭绝星辰 所有, 如有侵权,请联系我们删除。