一、PCIe简介

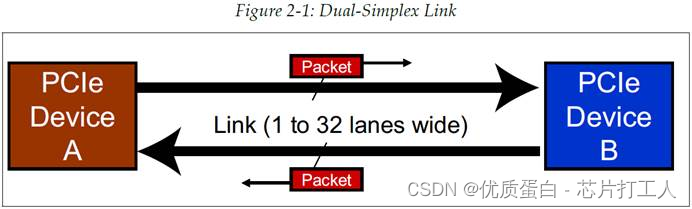

PCIe是一种串行总线,采用双向连接的方式,可同时收发,是一种双单工连接。

PCIe设备之间的信号传输路径称作链路(Links),一个link由一个或多个收发通道(Lanes)组成。协议规范中的x1、x2、x4、x8、x16和x32分别表示一个link中包含1、2、4、8、16或32个lane。PCIe 允许多种链路宽度,系统设计时可以在成本和性能之间做出适当的权衡——采用更多的lane可以提供更高的通信带宽,但成本、空间和功耗相应增加。

1.1 串行传输

1.1.1 相对于并行传输的优化

并行传输的不足:

- 并行传输中参考时钟存在时钟偏斜,即时钟在发送方和接收方的时刻不同;

- 并行传输中多比特信号之间可能存在数据偏斜,即多比特信号到达和稳定的时刻不同。

串行传输的克服了上述不足。串行传输将时钟信号包含于数据流中,无需额外的传输线来传输参考时钟。因此,即使数据传输的时长跨越多个时钟周期也不会导致数据相对于参考时钟的滞后,也便不存在时钟偏斜的问题。串行传输中单通道单次传输单比特信号,也不存在数据偏斜的问题(多通道设计中需要引入对齐机制)。

1.1.2 带宽计算

- PCIe 1.x比特率为2.5GT/s,采用8b/10b编码,每个lane的带宽计算方法为:

带宽 =(2.5GT/s x 2 双向)/ 10bits per symbol = 0.5GB/s

- PCIe 2.x比特率为5.0GT/s,采用8b/10b编码,每个lane的带宽计算方法为:

带宽 =(5.0GT/s x 2 双向)/ 10bits per symbol = 1GB/s

- PCIe 3.x比特率为8.0GT/s,采用128b/130b编码(2比特的开销忽略不计),每个lane的带宽计算方法为:

带宽 ≈(8.0GT/s x 2 双向)/ 8 bits per symbol = 2GB/s

PCIe 3.x之后的规范版本带宽计算方法类似,故不再此赘述。上述每个lane的带宽乘以链路宽度即可得到链路的总带宽。

PCIe各版本规范特性

版本1.X2.X3.X4.05.06.0发布年份200320072010201720192022编码方式8b/10b8b/10b128b/130b128b/130b128b/130b1b/1b比特率(GT/s/lane)2.558163264带宽(GB/s/lane)0.5124816

1.1.3 差分信号传输

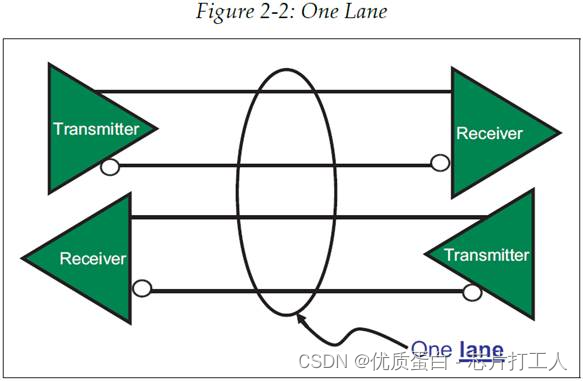

PCIe总线中每个lane都采用差分信号进行传输,包含一对发送差分信号对和一对接收差分信号对这样会导致设备的引脚数增加一倍,但其收益非常明显:提高噪声容限、降低信号电压。

接收端在接收到差分信号时,将正信号的电压与反信号的电压相减得到差值后进行电平判定。差分信号的正反信号传输线走线非常靠近,且设备引脚相邻,当其中一路信号受到外界干扰时另一路信号必然同时受到干扰,两路信号同时受到相似的干扰反映到差值上时可忽略不计。

1.1.4 基于数据包的传输协议

将并行传输转变为串行传输可以极大的减少数据传输需要的引脚数量,也减少了额外的边带信号来指示控制信息。PCIe中定义了传输事务数据包(Packets)的结构,该结构中包含了事务类型等关键信息,接收方可以通过解析数据包来获取传输事务的类型,从而获悉需要执行什么操作。

1.2 PCIe的系统拓扑结构

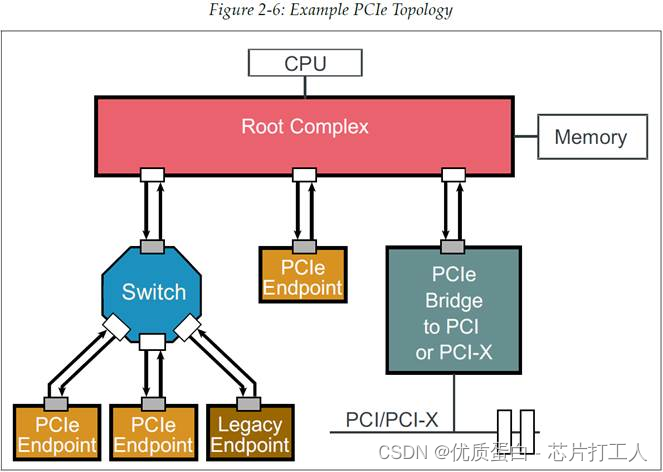

一条 PCIe 链路必须是一个点对点的连接,但可以通过通过交换机(Switches)和桥(Bridges)来构建灵活的系统拓扑,下图为一个简单的示例。

PCIe只允许树结构,不允许出现循环或其他复杂拓扑结构,这么做是为了保持与PCI软件的向后兼容性。CPU通常为PCIe层次结构的顶端。

1.2.1 根组件(Root Complex,RC)

CPU与PCIe总线之间的接口可能包含一系列的组件(处理器接口,DRAM 接口等等),甚至是包含多个芯片。将这些组件合起来,称这一组组件为根组件(Root Complex,RC,Root),位于树状拓扑的“根部”,并代表 CPU 与系统的其余部分通信。

1.2.2 上行端口与下行端口

- 上行端口(Upstream Port)指的是拓扑结构的向上的端口,如图中endpoint向上连接switch的端口,PCIe中的设备必须且仅能有1个上行端口;

- 下行端口(Downstream Port)与上行端口在拓扑意义上相反,PCIe中的设备必可以有若干个下行端口。

1.2.3 交换机与桥 (Switches and Bridges)

- 交换机(Switches)使得单个 PCIe 端口上可以连接更多的设备,它作为数据包的路由器,可根据数据包提供的路由信息来识别其路由路径。Switch可以有若干个下行端口;

- 桥(Bridges)提供了一个通往其他总线的接口,例如 PCI 或者 PCI-X,或其他的 PCIe 总线。

1.2.4 端点(Endpoints)

Endpoints是系统中即不是switches也不是bridges的设备,位于树状拓扑分支底部,只能有1个上行端口。Endpoints可以作为总线上事务的发起者或完成者。

PCIe端点分为原生PCIe端点(Native PCIe Endpoints)和传统PCIe端点(Legacy PCIe Endpoints)。原生 PCIe 端点是从一开始就被设计用来在 PCIe 系统中使用的,是内存映射设备;而传统 PCIe 端点则是用于老式总线(例如 PCI-X)的设备,在PCIe系统中可能使用了在 PCIe 设计中被禁止的东西,例如 IO 空间、支持 IO 事务以及支持锁定请求,在此暂不讨论。

下篇:PCIe学习笔记2:PCIe体系架构——PCIe设备层次

版权归原作者 优质蛋白 - 芯片打工人 所有, 如有侵权,请联系我们删除。